FPGA基数控延时器设计:计数器串联与资源优化

55 浏览量

更新于2024-08-28

收藏 370KB PDF 举报

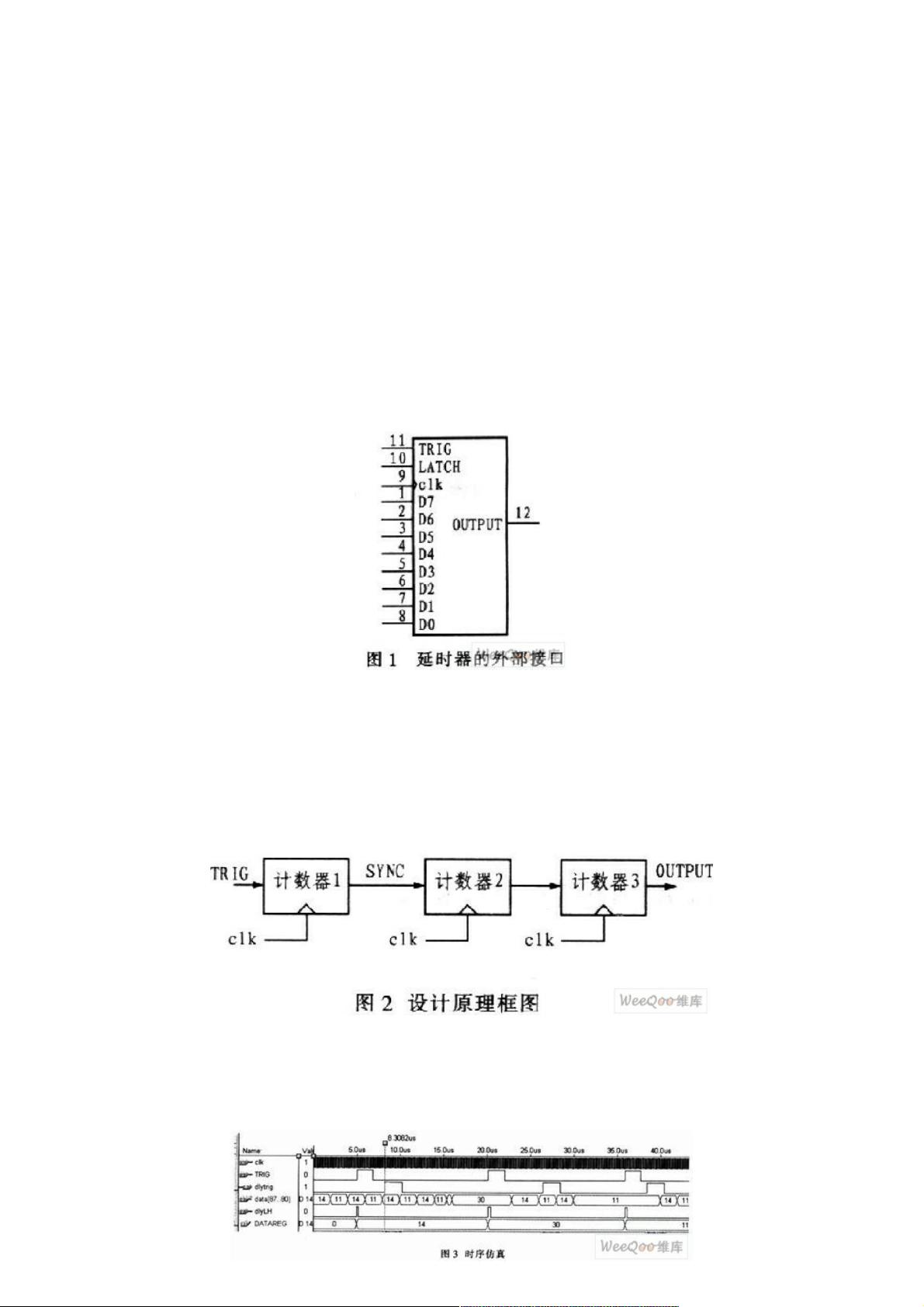

基于现场可编程门阵列(FPGA)的数控延时器是一种创新的数字电路设计,它利用硬件描述语言VHDL和可编程逻辑器件(PLD)技术来实现高灵活性和定制化的延时功能。设计的核心思想是通过串联多个计数器来控制延时时间,计数器1产生同步脉冲SYNC,作为触发信号,计数器2负责存储和管理延时量,而计数器3则用于确定输出脉冲OUTPUT的宽度。

延时器设计的关键步骤包括以下几个部分:

1. **计数器串联**:设计中采用3个计数器串联工作模式,这样可以根据需要设置不同的延时范围。计数器1负责生成同步脉冲,当接收到时钟clk的上升沿时计数,产生的SYNC信号触发后续计数过程。

2. **延时控制**:当接收到8位数据线的延时量后,计数器2根据这个值进行计数,直到达到设定的时间后,触发LATCH的高电平,将延时数据锁存起来。计数器3则在此过程中同步计数,以确保输出脉冲的精确宽度。

3. **延时精度**:设计中考虑了延时误差分析,通过精确的计数逻辑和合理的资源分配,力求减小延时误差。延时度的控制是通过调整计数器的配置和时钟频率来实现的。

4. **外部接口**:设计模仿AD9501的标准接口,使得延时器能够方便地与其他电路集成。外部接口电路包括输入延时量的8位数据线、触发脉冲TRIG、同步脉冲SYNC、以及输出脉冲OUTPUT。

5. **应用环境**:该设计应用于雷达目标模拟器的控制部分,与Altera公司生产的EPFl0K30AQC208-3型号的专用电路和DSP集成,用于模拟目标距离,这体现了延时器在实际系统中的实用价值。

6. **软硬件开发**:软件编程和调试在MuxplusⅡ环境下完成,确保了系统的稳定性和可调试性。

基于FPGA的数控延时器设计提供了一种高效、灵活且精确的延时解决方案,适用于需要精确控制延时时间和响应速度的电子系统,如雷达和模拟器等应用领域。

127 浏览量

2021-05-18 上传

129 浏览量

129 浏览量

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

127 浏览量

weixin_38643127

- 粉丝: 8

- 资源: 920

最新资源

- jquery开关按钮基于Bootstrap开关按钮特效

- merkle-react-client:客户

- 财务管理系统javaweb项目

- DOM-Parsing:DOM解析和序列化

- FastReport v6.7.11 Enterprise installer .zip

- pid控制器代码matlab-AutomatedBalancingRobot:自动平衡机器人是一个项目,其中建造了一个两轮机器人,并将其编程为

- 基于MATLAB模型设计的FPGA开发与实现.zip_UBK_matlab与fpga_simulink模型_struck9hw_

- ubiq:基于HugSQL和GraphQL的Web应用程序,移动部分最少

- 行业文档-设计装置-一种折叠式防滑书立.zip

- 意法半导体参考文献及软件资料.7z

- LoRa-High-Altitude-Balloon:这是蒙大拿州立大学LoRa小组顶峰项目的存储库,该项目是蒙大纳州太空资助财团BOREALIS实验室的项目。 以下代码在定制板上运行,该定制板上旨在收集高空气球有效载荷上的大气数据

- BW_Anal-开源

- nuaa_check_action:inuaa打卡,基于GitHub Action的南航校内,校外打卡

- alex_presso

- perf:PERF是详尽的重复查找器

- 行业文档-设计装置-一种折叠式包装纸箱.zip