数字集成电路设计:组合逻辑电路深度解析

需积分: 8 149 浏览量

更新于2024-08-11

1

收藏 371KB PDF 举报

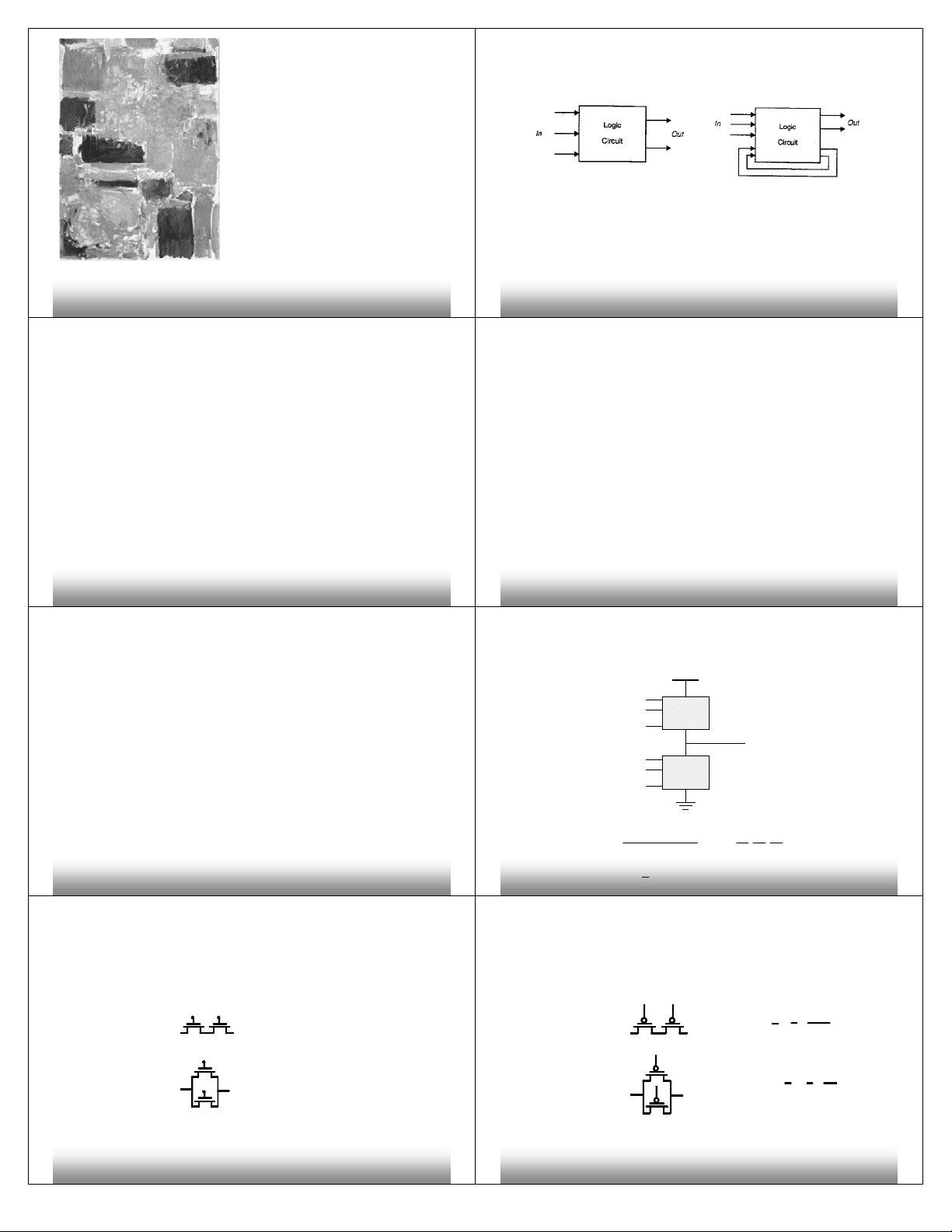

"这篇文档是关于数字集成电路设计的,特别是关注组合逻辑电路的初步介绍。文档探讨了组合逻辑电路和时序逻辑电路的区别,并详细阐述了组合逻辑的特点,如输出只依赖于当前输入,无反馈到输入端,以及常用的设计评估标准。此外,文档还提到了静态CMOS技术,包括其工作原理、优点和结构,以及静态CMOS中的互补逻辑和传输逻辑概念。"

本文档主要涵盖了以下几个关键知识点:

1. **组合逻辑电路与时序逻辑电路**:

- 组合逻辑电路的输出仅取决于当前的输入信号,由布尔函数决定,不存在记忆功能。

- 时序逻辑电路则不仅考虑当前输入,还依赖于电路先前的状态,即前一个输入的值。

2. **组合逻辑电路的基本特性**:

- 输出与输入之间存在即时的关系,没有反馈路径。

- 常见的简单电路如反相器,以及更复杂的门电路如NAND和NOR门。

- 设计评价指标包括电路面积、速度、能量消耗和功耗,以及噪声抵抗能力和可靠性。

3. **静态CMOS电路**:

- 静态CMOS电路始终输出布尔函数值,除非在开关瞬间。

- 输出总是连接到电源VDD或地VSS,除非在瞬态过程中。

- 电路结构简单,寄生效应小,速度较快,但容易受到噪声影响。

4. **静态CMOS的互补逻辑**:

- 静态CMOS电路中,上拉网络(PUN)和下拉网络(PDN)形成对等逻辑网络,实现逻辑运算。

- PMOS和NMOS晶体管作为栅控开关,分别在高电平和低电平时导通,用于传递强0和弱1。

5. **NMOS和PMOS晶体管**:

- NMOS晶体管在栅极输入高电平时导通,常用于实现逻辑“与”和“或”操作。

- PMOS晶体管则在栅极输入低电平时导通,通常用于传递强1,实现逻辑“与非”和“或非”操作。

这篇文档对于理解数字集成电路中的基本逻辑构造及其工作原理提供了很好的基础,特别适合初学者和对数字集成电路设计感兴趣的读者。通过深入学习这些内容,可以为进一步研究数字系统设计、逻辑优化和集成电路实现打下坚实的基础。

2021-05-21 上传

2021-05-24 上传

2021-05-24 上传

2021-05-21 上传

2021-05-21 上传

2021-05-25 上传

点击了解资源详情

2024-11-29 上传

2024-11-29 上传

2024-11-29 上传

weixin_38732277

- 粉丝: 7

- 资源: 880

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍