数字集成电路设计:组合逻辑电路的无源与有源负载分析

需积分: 5 194 浏览量

更新于2024-08-11

1

收藏 902KB PDF 举报

"本文档主要探讨了数字集成电路中的组合逻辑电路,特别是从设计的角度出发,讲解了比例逻辑的概念,包括无源负载和有源负载两种实现方式,以及准NMOS的特点和潜在问题。"

组合逻辑电路是数字集成电路设计的基础部分,它们由一系列逻辑门组成,其输出仅依赖于当前的输入状态,不具有记忆功能。本资料深入浅出地分析了组合逻辑电路的设计策略,特别是在减少晶体管数量和优化性能方面。

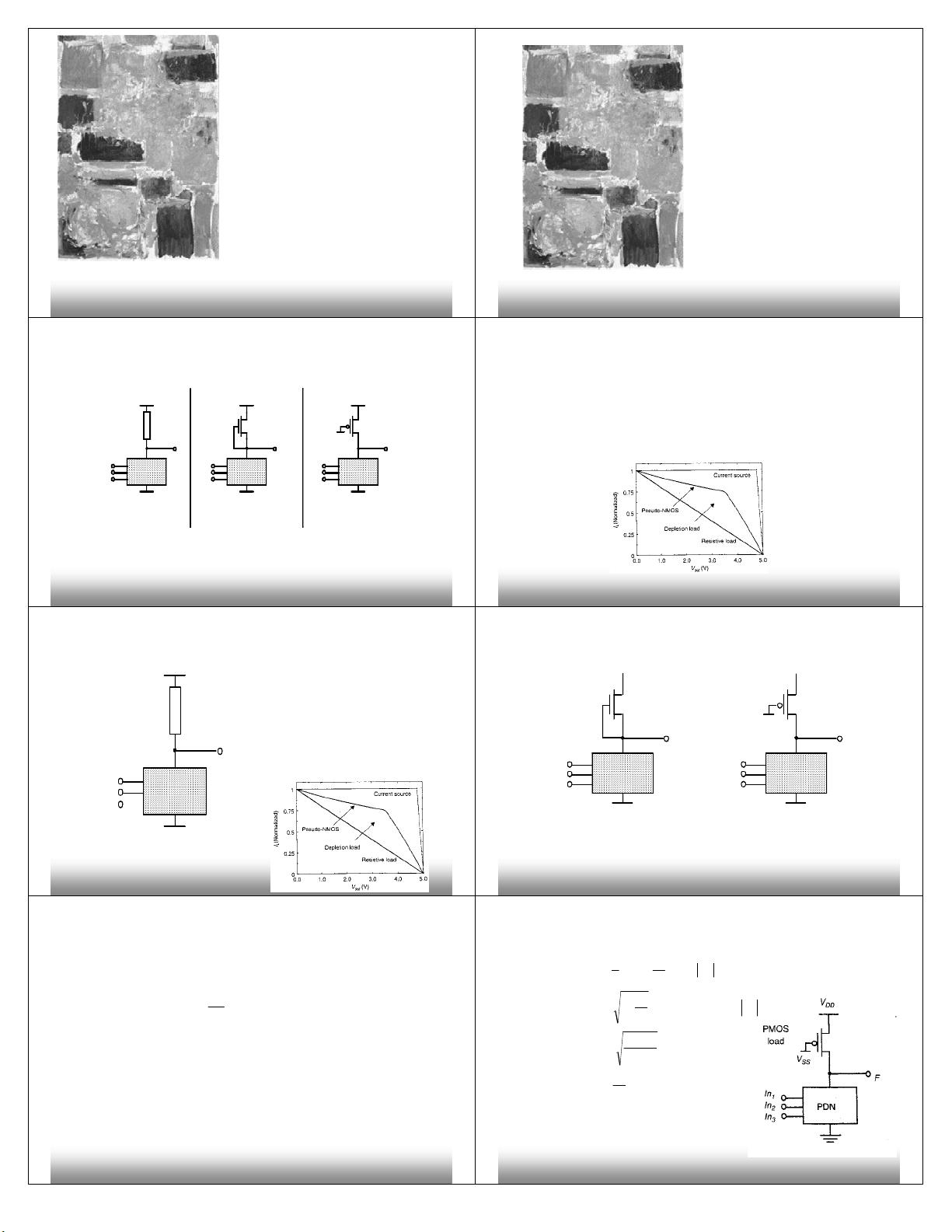

比例逻辑是一种旨在减少晶体管数量的设计方法。它通过利用部分导通的PDN(Power Domain Network)与上拉电阻共同分压,来实现输出电压与输入信号之间的比例关系。当PDN关闭时,上拉电阻确保输出电压VOH等于VDD;当PDN打开时,上拉电阻和PDN形成分压,从而实现比例逻辑。这种设计可以降低静态功耗,但同时也可能导致输出电压的不对称响应。

文档提到了两种无源负载比例逻辑的实现方式:电阻负载和耗尽NMOS负载。电阻负载虽然简单,但会导致不对称的输出电压响应和静态功耗。而耗尽NMOS负载可以提供更对称的响应,但其上升和下降延时可能不同,并且依然存在静态功耗。

有源负载比例逻辑则使用了准NMOS技术,这里的负载PMOS接地,使其更接近理想的电流源,同时由于没有体效应,相同尺寸的准NMOS可以提供更大的电流,这对于处理大扇入的复杂门电路非常有用。然而,准NMOS也存在上升和下降延时不对称、VTC(阈值电压-电流特性)不对称的问题,尽管其减少了面积和负载,但静态功耗仍然是一个挑战。

总结来说,该文档提供了关于数字集成电路设计中组合逻辑电路和比例逻辑的详细见解,涵盖了无源和有源负载的选择,以及准NMOS的优势和局限性。这些内容对于理解数字集成电路设计原理和优化方法具有重要的参考价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-05-21 上传

2021-05-24 上传

2021-05-24 上传

2021-05-21 上传

2021-05-21 上传

2021-05-25 上传

weixin_38614484

- 粉丝: 0

- 资源: 874

最新资源

- Variational-AutoEncoder-For-Novelty-Detection:使用Keras实现的变体自动编码器,用于对EMNIST-Letters数据集执行新颖性检测

- js透明按钮图片滑动切换焦点图

- trabajo-2bim-001-iaortiz:GitHub Classroom创建的trabajo-2bim-001-iaortiz

- coinhsl依赖文件

- 行业资料-电子功用-具有对数自保护功能的高压总线放电电路的说明分析.rar

- 【WordPress插件】2022年最新版完整功能demo+插件.zip

- 【推荐】海康威视-综合安防系统设计方案-HIK-201707V2.1

- CSP-J组复赛第二题 公路附件

- T.O.P Big Bang Wallpaper for New Tab-crx插件

- tutorials:来自SciPy和PyData会议的可执行教程的集合

- 行业资料-电子功用-具有对正导向件的电连接器的说明分析.rar

- 异步电机仿真模型.7z

- 彩绘快餐店菜单设计矢量

- IOS应用源码Demo-日历组件-毕设学习.zip

- 基于java-136_基于Java的酒店管理系统的设计与实现-源码.zip

- DownloadFilesWithThreadPoolExecutor