FPGA驱动的便携式高速数字示波器设计

160 浏览量

更新于2024-08-31

收藏 408KB PDF 举报

"基于FPGA的简易可存储示波器设计"

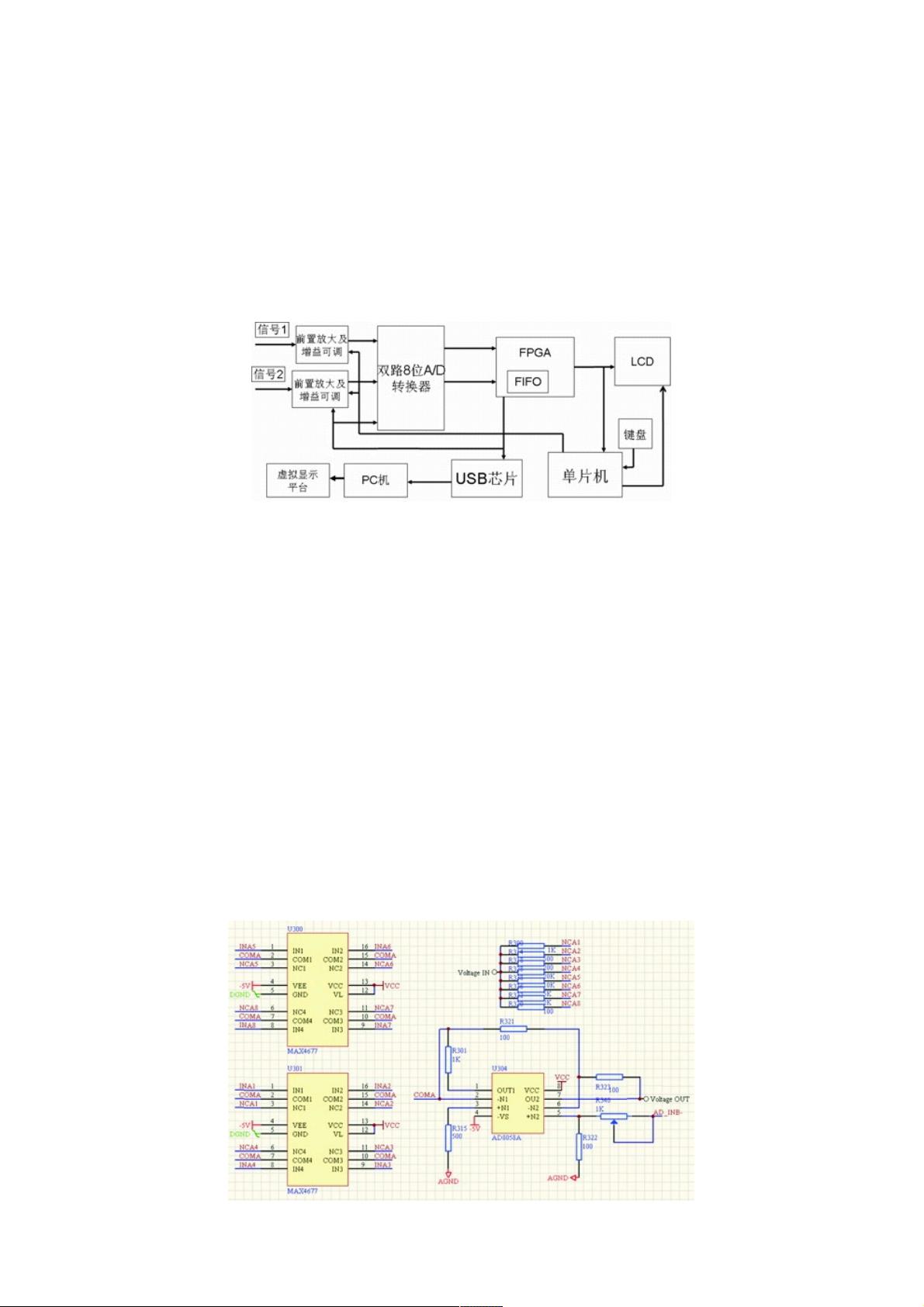

本文主要探讨了一种基于现场可编程门阵列(FPGA)技术的高速、便携式数字示波器设计,该示波器具备双通道数据采集能力,最高采样速度达到60Mbit/s,并能实现自动量程和采样频率调整,数据缓存,显示功能以及与计算机的数据交互。

首先,设计背景提及传统示波器存在的局限性,如体积大、成本高,这促使了便携式数字存储采集器的发展。这种新型示波器利用了诸如液晶显示、高速模拟/数字(A/D)转换和专用集成电路(ASIC)等先进技术,以实现更高的实用性和市场竞争力,符合现代电子测量设备小型化、多功能化的趋势。

系统构成主要包括以下几个关键部分:

1. 高速数据采集模块:系统采用双通道同步数据采集,每个通道都配备了独立的采样保持器和A/D转换器,确保数据采集的精确同步。MAX1197型A/D转换器因其高速性能(60Mbit/s)、低功耗和小尺寸被选中,其内置的采样保持器能有效处理高速信号。

2. 信号调理电路:为了适应不同电压范围的测量,设计中采用了可调增益电路和分压器。示波器探头与分压器结合,使得输入信号可以衰减至适合A/D转换器的电压范围。同时,系统还包含了过载保护电路,通过二极管和电阻限制输入信号在±4.8V的安全范围内,防止器件受损。

3. 阻抗变换与增益调节:高输出阻抗的信号需要通过阻抗变换器转变为低输出阻抗,以减少信号失真。这里采用的是AD8065 FET输入单电压反馈放大器,构建跟随器进行阻抗变换。随后,通过模拟开关和宽带精密放大器配合,实现增益调节,确保信号适应A/D转换器的输入要求。

4. 数据缓存与传输:采集的数字信号被暂存在FPGA内的FIFO缓存中,然后通过USB接口传送到计算机,进行进一步的数据处理或在液晶屏幕上实时显示。这一过程实现了数据的实时处理和分析,增强了示波器的功能性。

该基于FPGA的简易可存储示波器设计充分利用了FPGA的灵活性和高速处理能力,实现了高精度、高效率的信号采集与处理,同时具备良好的用户交互界面,是现代电子测量技术的一次创新。这样的设计不仅简化了传统示波器的复杂性,而且提高了测量的便捷性和可靠性,为电子工程和科研领域提供了新的工具选择。

点击了解资源详情

191 浏览量

270 浏览量

213 浏览量

191 浏览量

2021-07-13 上传

2021-07-13 上传

160 浏览量

121 浏览量

weixin_38628830

- 粉丝: 3

最新资源

- DeepFreeze密码移除工具6.x版本使用教程

- MQ2烟雾传感器无线报警器项目解析

- Android实现消息推送技术:WebSocket的运用解析

- 利用jQuery插件自定义制作酷似Flash的广告横幅通栏

- 自定义滚动时间选择器,轻松转换为Jar包

- Python环境下pyuvs-rt模块的使用与应用

- DLL文件导出函数查看器 - 查看DLL函数名称

- Laravel框架深度解析:开发者的创造力与学习资源

- 实现滚动屏幕背景固定,提升网页高端视觉效果

- 遗传算法解决0-1背包问题

- 必备nagios插件压缩包:实现监控的关键

- Asp.Net2.0 Data Tutorial全集深度解析

- Flutter文本分割插件flutter_break_iterator入门与实践

- GD Spi Flash存储器的详细技术手册

- 深入解析MyBatis PageHelper分页插件的使用与原理

- DELPHI实现斗地主游戏设计及半成品源码分析