CPLD/FPGA多串口扩展:提升工业控制通信效率与集成性

141 浏览量

更新于2024-08-31

收藏 288KB PDF 举报

在当前工业控制领域,一对多串口通讯的可靠性和系统集成性是关键挑战。本文针对这一需求,提出了一种基于CPLD (Complex Programmable Logic Device) 和 FPGA (Field-Programmable Gate Array) 的多串口设计解决方案。通过嵌入式技术的应用,该设计旨在简化硬件电路,降低系统成本,提高系统的灵活性和可靠性。

首先,文章的重点在于利用CPLD/FPGA的并行处理能力,实现从并行总线接口到多个全双工异步串行通讯口(如RS232)的高效转换。每个串口接收器配备8个接收缓冲单元,这显著提升了高速嵌入式CPU与外部设备之间的数据传输速率匹配,确保了实时通信性能。此外,设计允许用户根据实际需求调整串口波特率和其他参数,提供了极高的可定制性。

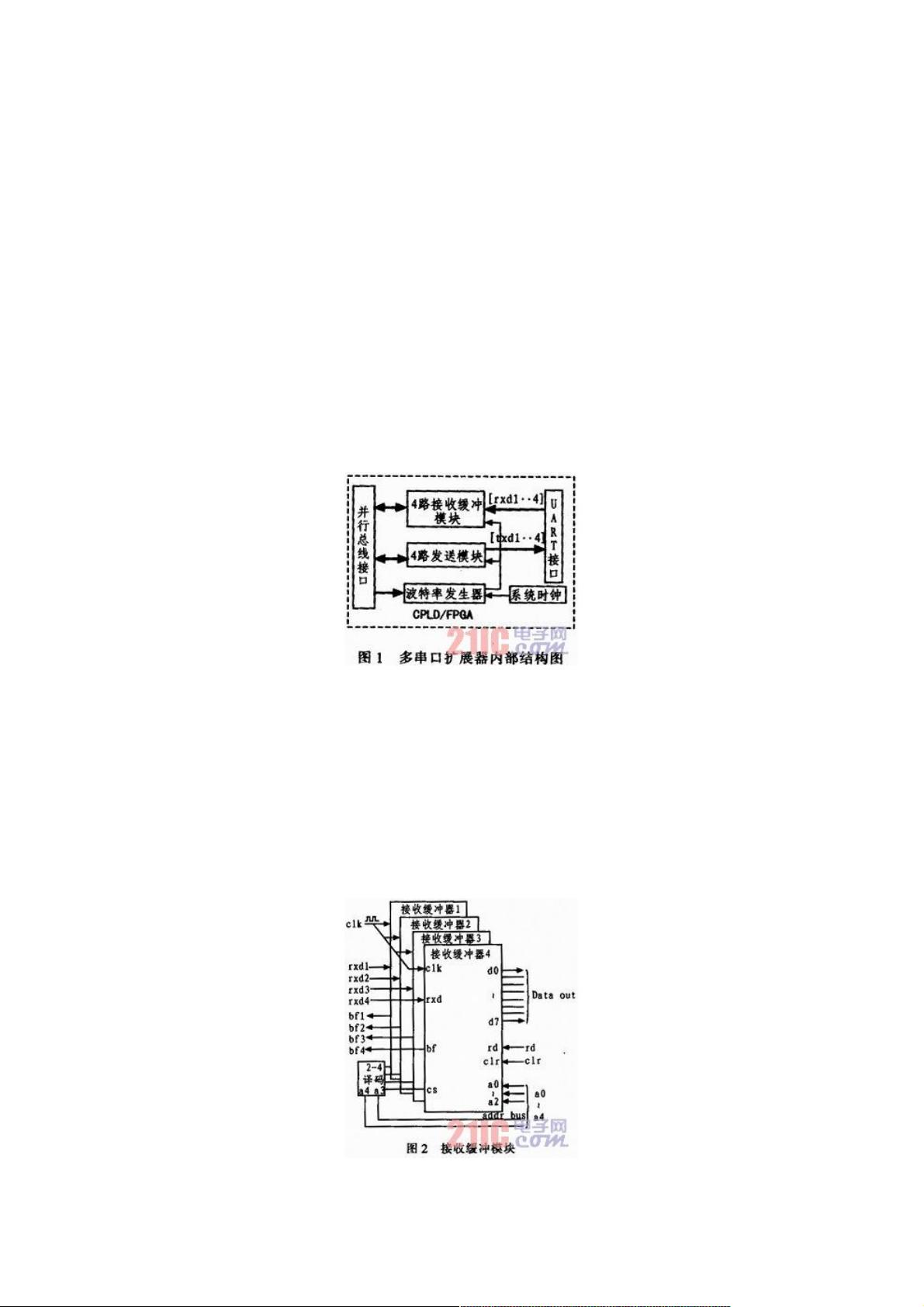

系统的核心是CPLD/FPGA芯片,它负责并行总线的管理和多串口的扩展。4路接收缓冲器、4路发送器、波特率发生器和UART接口构成核心功能模块,使得系统能够同时处理多个设备的通信。波特率发生器使用外部有源晶振提供时钟信号,通过精确选择晶振频率,确保了数据传输的稳定性和效率。

接收缓冲模块是设计中的关键技术之一,它包括4个独立的缓冲器,每个都有自己的rxd、bf、cs引脚,分别用于串行数据输入、接收状态检测和选择特定缓冲器。这种设计提高了数据处理的灵活性,降低了冲突概率,从而提高了串口通讯的可靠性。

本文的基于CPLD/FPGA的多串口设计为工业控制中的串口通讯提供了一个有效且集成的解决方案,它优化了系统架构,提升了通信性能,满足了对串口通讯质量和系统集成度的高要求。通过实际应用验证,这种设计已经成功地适应了工业控制环境,并展示了其在复杂环境中的一对多串口通讯方面的优势。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38653878

- 粉丝: 1

- 资源: 940

最新资源

- JHU荣誉单变量微积分课程教案介绍

- Naruto爱好者必备CLI测试应用

- Android应用显示Ignaz-Taschner-Gymnasium取消课程概览

- ASP学生信息档案管理系统毕业设计及完整源码

- Java商城源码解析:酒店管理系统快速开发指南

- 构建可解析文本框:.NET 3.5中实现文本解析与验证

- Java语言打造任天堂红白机模拟器—nes4j解析

- 基于Hadoop和Hive的网络流量分析工具介绍

- Unity实现帝国象棋:从游戏到复刻

- WordPress文档嵌入插件:无需浏览器插件即可上传和显示文档

- Android开源项目精选:优秀项目篇

- 黑色设计商务酷站模板 - 网站构建新选择

- Rollup插件去除JS文件横幅:横扫许可证头

- AngularDart中Hammock服务的使用与REST API集成

- 开源AVR编程器:高效、低成本的微控制器编程解决方案

- Anya Keller 图片组合的开发部署记录