CPLD/FPGA实现的多串口扩展技术

需积分: 10 15 浏览量

更新于2024-09-10

2

收藏 275KB PDF 举报

"基于CPLD/FPGA的多串口设计与实现"

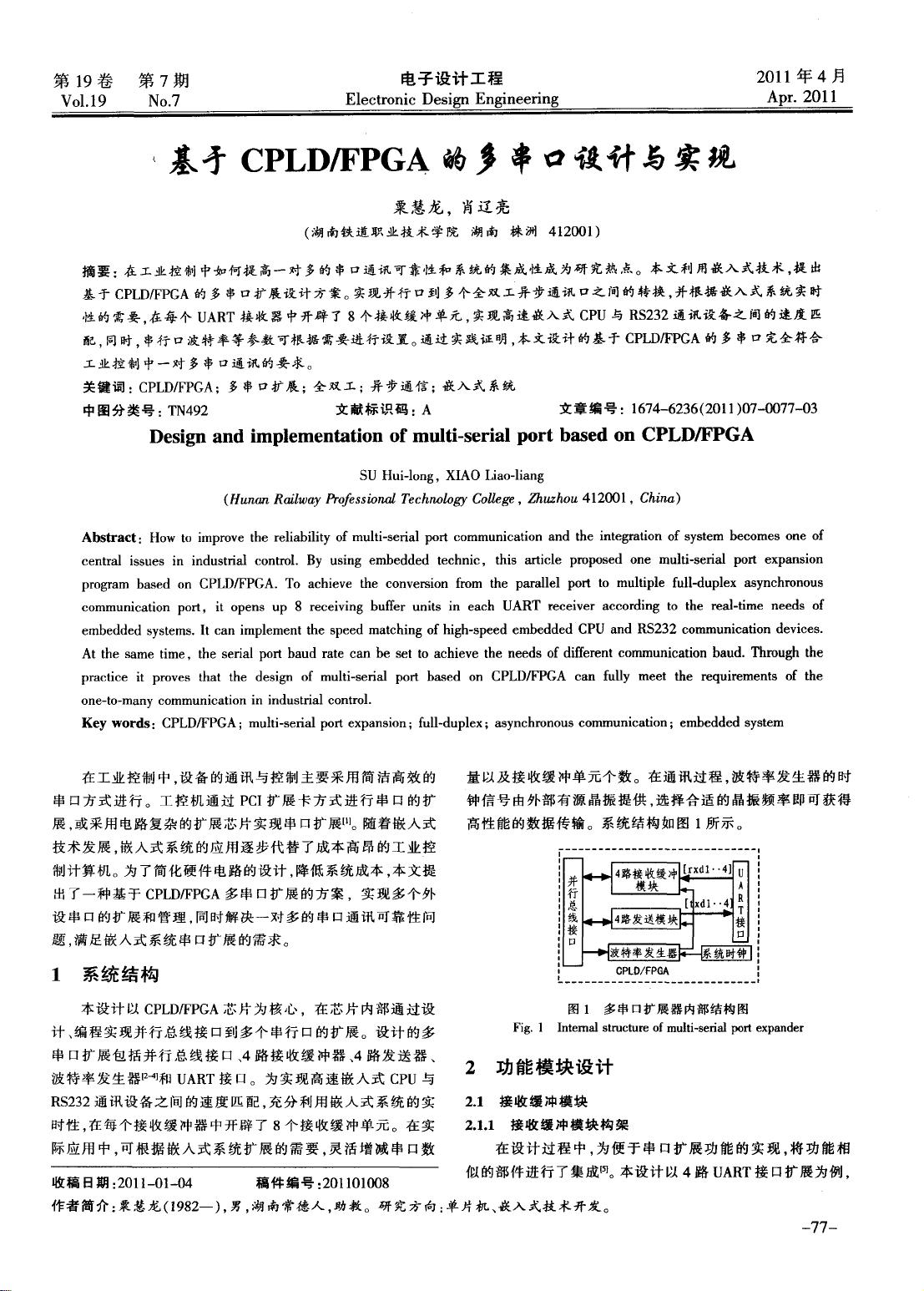

在现代工业控制领域,提高一对多串行通信的可靠性和系统集成性是关键的技术挑战。本文介绍了一种利用CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)实现的多串口扩展设计方案,旨在解决这一问题。该方案能够将并行12位数据接口转换为多个全双工异步通信端口,以适应嵌入式系统实时性的需求。

设计的核心在于CPLD/FPGA的灵活配置能力,它们可以被编程来实现复杂的逻辑功能,如数据路由、波特率发生器以及串行/并行转换。通过在每个UART(通用异步收发传输器)接收器内部设置8个接收缓冲单元,该设计能够有效地匹配高速嵌入式CPU与RS232通信设备之间的数据速率差异,确保数据传输的稳定性和效率。

串行通信的波特率、校验位、停止位等关键参数可以根据实际应用需求进行设置,这增加了设计的灵活性。这样的设计使得系统能够适应各种不同的通信标准和协议,增强了其在不同工业环境中的适应性。

FPGA在其中扮演的角色主要是提供高速的数据处理能力,而CPLD则用于实现逻辑控制和接口复用。两者结合,能够实现对多个串口的高效管理,减少硬件资源的占用,同时提高系统的响应速度和处理能力。

在实际应用中,基于CPLD/FPGA的多串口设计经过验证,完全满足了工业控制环境中一对多串口通信的需求。这种设计不仅提高了通信的可靠性,还简化了系统架构,降低了硬件成本,对于工业控制系统的优化和升级具有重要意义。其涉及到的关键技术包括CPLD/FPGA的硬件描述语言编程、串行通信协议的理解和实现、以及嵌入式系统实时性要求的满足策略。

这篇文章详细探讨了如何利用CPLD/FPGA技术来设计和实现一个高效的多串口扩展系统,这对于工业控制领域的工程师和技术人员来说,是一个极具价值的参考资源。通过这种设计,可以显著提升系统性能,增强系统的扩展性和适应性,为工业控制领域的串行通信提供了一个强大的解决方案。

170 浏览量

点击了解资源详情

点击了解资源详情

170 浏览量

142 浏览量

2020-08-13 上传

142 浏览量

201 浏览量

点击了解资源详情

foolqiang

- 粉丝: 4

- 资源: 15

最新资源

- torch_cluster-1.5.6-cp36-cp36m-linux_x86_64whl.zip

- D-无人机:拉无人机。 使用计算机视觉在喷漆墙上画画以实现精确导航

- myloader

- Metro_Jiu-Jitsu-crx插件

- 导航条,鼠标悬停滑动下拉二级导航菜单

- 中国企业文化理念:提炼与实施的流程及方法(第一天课程大纲)

- 使用videojs/aliplayer 实现rtmp流的直播播放

- irt_parameter_estimation:基于项目响应理论(IRT)的物流项目特征曲线(ICC)的参数估计例程

- visualvm_21.rar

- torch_sparse-0.6.4-cp38-cp38-linux_x86_64whl.zip

- redratel:数字代理

- JumpStart!-开源

- api-2

- Adoptrs-crx插件

- redis windows x64安装包msi格式的

- XX轧钢企业文化诊断报告