Xilinx UltraScale架构:ASIC和SoC原型验证的理想解决方案

版权申诉

118 浏览量

更新于2024-09-07

收藏 1.21MB DOCX 举报

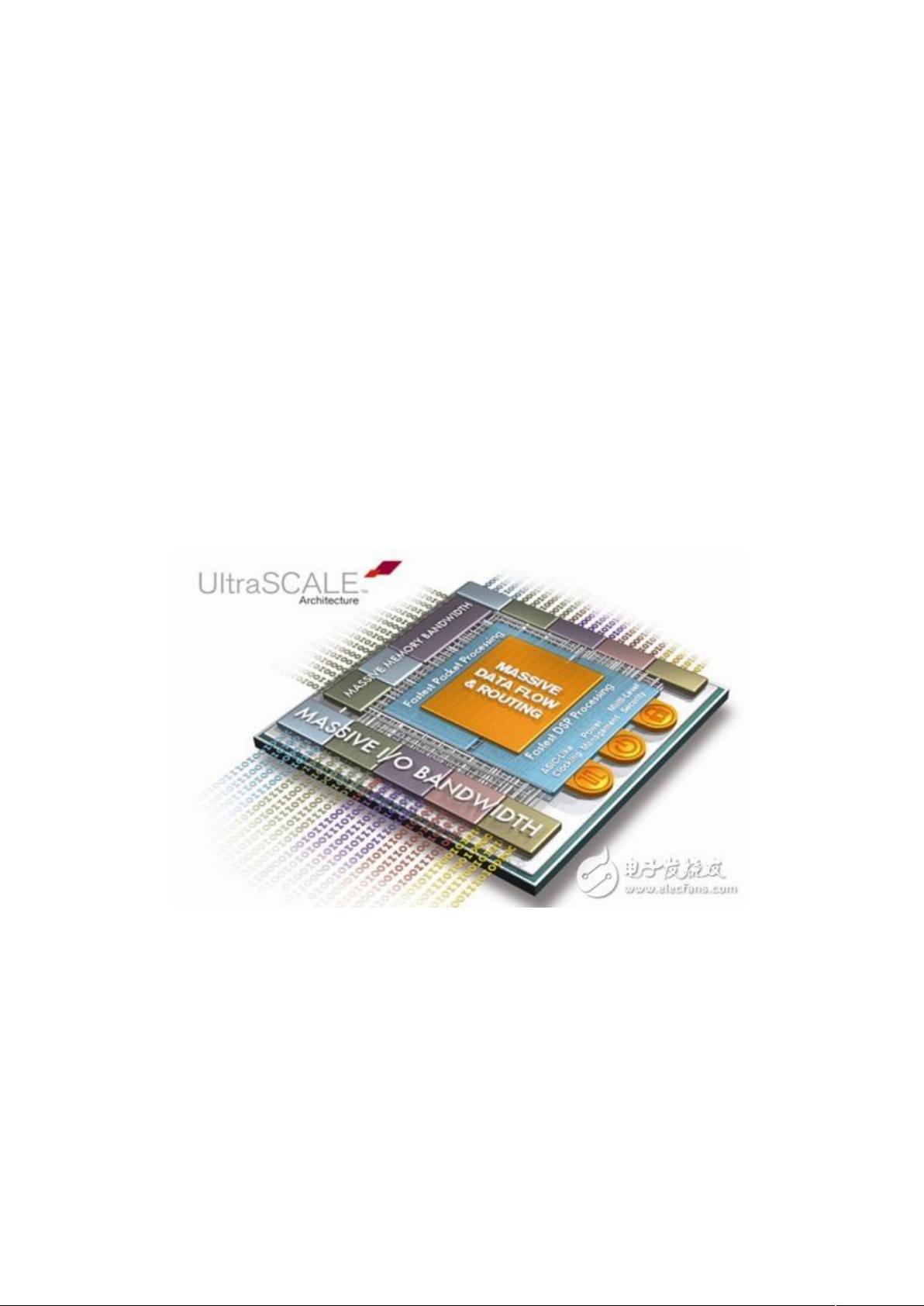

"Xilinx的新一代UltraScale架构被广泛认可为ASIC或System-on-Chip (SoC) 原型验证的理想选择,尤其是在应对大规模设计挑战时。这一架构以其高效能、低功耗和灵活的I/O特性,显著降低了开发风险和硬件需求。DiniGroup作为领先的FPGA验证平台供应商,推出了基于Xilinx UltraScale的DNVUF4A平台,提供超大规模的ASIC原型验证解决方案,可扩展至超过10亿门的设计。”

Xilinx UltraScale架构是针对日益复杂的ASIC和SoC设计而开发的,它解决了传统单颗FPGA无法承载大规模逻辑设计的问题。通过20纳米工艺技术,Virtex UltraScale VU440 FPGA提供了数百万逻辑单元,使得设计师能够在单一芯片上处理千万门级乃至上亿门级的设计,有效避免了多芯片分区带来的复杂性和潜在风险。

UltraScale架构的亮点包括:

1. **高密度逻辑集成**:VU440 FPGA具有极高的逻辑门数,使得大型设计能在单个器件内实现,简化了设计流程和硬件配置。

2. **减少开发风险**:通过更早的原型验证,设计师可以更快地发现和修复设计错误,降低ASIC和ASSP设计的开发风险。

3. **节省板级空间**:UltraScale架构优化了封装和互连,减少了所需的物理空间,同时降低了系统复杂性。

4. **灵活I/O**:支持灵活的接口配置,便于与其他设备的邻接和通信,增强了系统的可扩展性和兼容性。

5. **低功耗**:在保持高性能的同时,通过优化的架构设计实现了系统级功耗的降低。

DiniGroup的DNVUF4A平台充分利用了Xilinx UltraScale的优势,提供了一个完整的原型验证系统,配置有四个Virtex UltraScale VU440 FPGA,可以支持高达1.16亿门的设计。该平台支持多种通信方式,如PCIe Gen3、USB和以太网,并且可以通过级联实现更大规模的扩展。DNVUF4A的所有FPGA资源都可供用户自定义,适应各种应用需求。

DNVUF4A系统框图显示了其高度集成的特性,支持多板堆叠,利用Xilinx的16纳米Virtex UltraScale系列FPGA,实现了高门密度和高速目标时钟频率。这样的解决方案不仅满足了当前大规模ASIC原型验证的需求,也为未来更复杂的设计提供了强大的平台支持。

Xilinx UltraScale架构和DiniGroup的DNVUF4A平台共同构成了一个强大的工具链,助力于解决现代ASIC和SoC原型验证的挑战,加速软件和固件的开发进程,同时也为设计者提供了更高的效率和更低的成本。

2022-11-03 上传

2024-01-08 上传

2021-11-18 上传

2021-10-30 上传

2021-01-20 上传

2023-10-28 上传

2022-11-03 上传

2020-04-06 上传

2021-01-17 上传

ziyoudianzi15

- 粉丝: 0

- 资源: 2万+

最新资源

- 基于Python的豆瓣电影TOP250爬虫数据分析设计源码

- 基于LSTM神经网络的时间序列预测(Python完整源码和数据)

- eostokenranking:EOS链上的排名令牌列表

- Excel模板4-圆环饼图组合百分比图.zip

- cyTrie-开源

- 行业分类-设备装置-一种耐压瓦楞纸箱.zip

- ndovextract:弃用-替换为https

- gerrit-rabbitmq-plugin:业主的开发被冻结。 如果您想获得所有权或想继续在您的分叉公共存储库上进行开发,请与我联系

- 程序员的数学2_程序员的数学_programmer_

- AmbientIT-AdminUI

- 旅游注册.rar

- 基于SSM的电影购票系统设计源码

- OraDoc-开源

- 行业资料-建筑装置-带推动式开关的LED光源书写笔.zip

- matlab自相关代码-cupl:铜杯

- VectorCompare:节点模块以比较ES6中的向量