优化ASIC和SoC设计:嵌入式存储器IP的选择与影响

PDF格式 | 334KB |

更新于2024-08-28

| 76 浏览量 | 举报

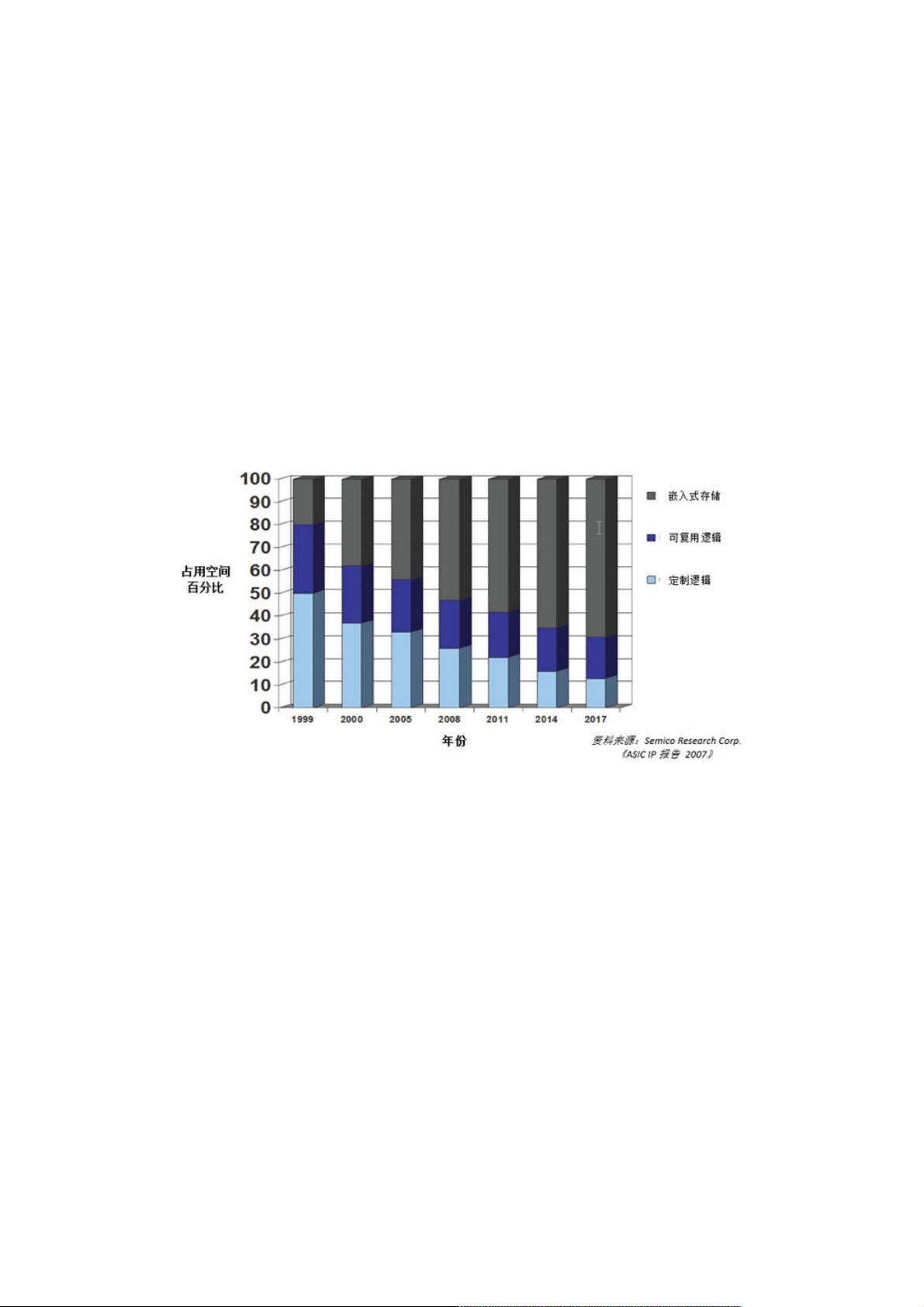

在现代ASIC和SoC设计中,嵌入式存储器IP的选择成为关键因素。随着芯片市场竞争日益激烈,特别是无线通信技术的发展,如802.11n、蓝牙等,对定制逻辑的需求增长有限,而可复用逻辑(如USB、以太网和CPU/IP核)的占用空间相对稳定。相比之下,嵌入式存储器占据的芯片空间比例显著提升,据统计,到2013年,大部分SoC和ASIC设计中嵌入式存储器占比已经超过50%。

嵌入式存储器的设计目标包括优化速度、功耗、密度和非易失性特性,这取决于多种因素,如图3所示的五大关键因素:功率效率、数据传输速率、可靠性、存储密度和成本效益。设计师需要根据具体应用需求来平衡这些因素,选择最合适的存储器IP。例如,多核SoC中可能包含不同类型的存储器,如SRAM、DRAM、Flash等,每种都有其特定的性能特点和应用场景。

存储器IP的选择不仅仅是关于性能,还包括其兼容性、验证方法和支持的工具。存储器编译器能够根据设计需求自动生成优化过的存储器IP,同时,IP的验证流程也至关重要,确保其在实际应用中的稳定性和功能性。此外,考虑到成本因素,设计师需要在满足功能需求的同时,尽可能选择性价比高的存储器解决方案。

随着ASIC和SoC设计复杂性的增加,为嵌入式存储器IP做出明智选择是提高整体设计效率和产品质量的关键。设计师需要深入了解各种存储器技术,以便在有限的芯片空间内实现性能和成本的最佳平衡。因此,选择适合的嵌入式存储器IP不仅关乎产品竞争力,还直接影响到最终产品的市场定位和用户体验。

相关推荐

weixin_38745648

- 粉丝: 7

- 资源: 909

最新资源

- servo-example-0.5.2.zip

- net.tsinghua:针对清华学生的跨平台自动登录实用程序

- 49个苹果app图标 .sketch素材下载

- 基于HTML实现的仿享客零食网触屏版html5手机wap购物网站模板下载(css+html+js+图样).zip

- 单片机太阳能路灯控制系统仿真protues

- node-simple-deploy

- HWHelpNow:hwhelpnow.com官方GitHub Repo

- yii2-widgets:Yii Framework 2.0有用的小部件集合

- 易语言复制组件到选择夹子夹

- MDB_3.0,999玫瑰c语言表白源码,c语言

- dotfiles:每天使用.dotfiles

- storemate-backend-leveldb-0.9.23.zip

- 基于ASP.net数据存储与交换系统设计(源代码+论文).rar

- Javascript-30-WesBos

- 夸克:离线时保持快乐| 世界上第一个离线搜索引擎

- Recipes