FPGA基AGWN信号发生器:通信抗噪声设计与实现

150 浏览量

更新于2024-08-30

收藏 220KB PDF 举报

在EDA/PLD技术中,基于FPGA的加性高斯型白噪声(AGWN)信号生成器设计是一个关键的模块,特别是在通信系统抗噪声性能分析中起着至关重要的作用。AGWN信号通常作为理想信道噪声模型,用于评估接收信号的质量和系统的性能极限。

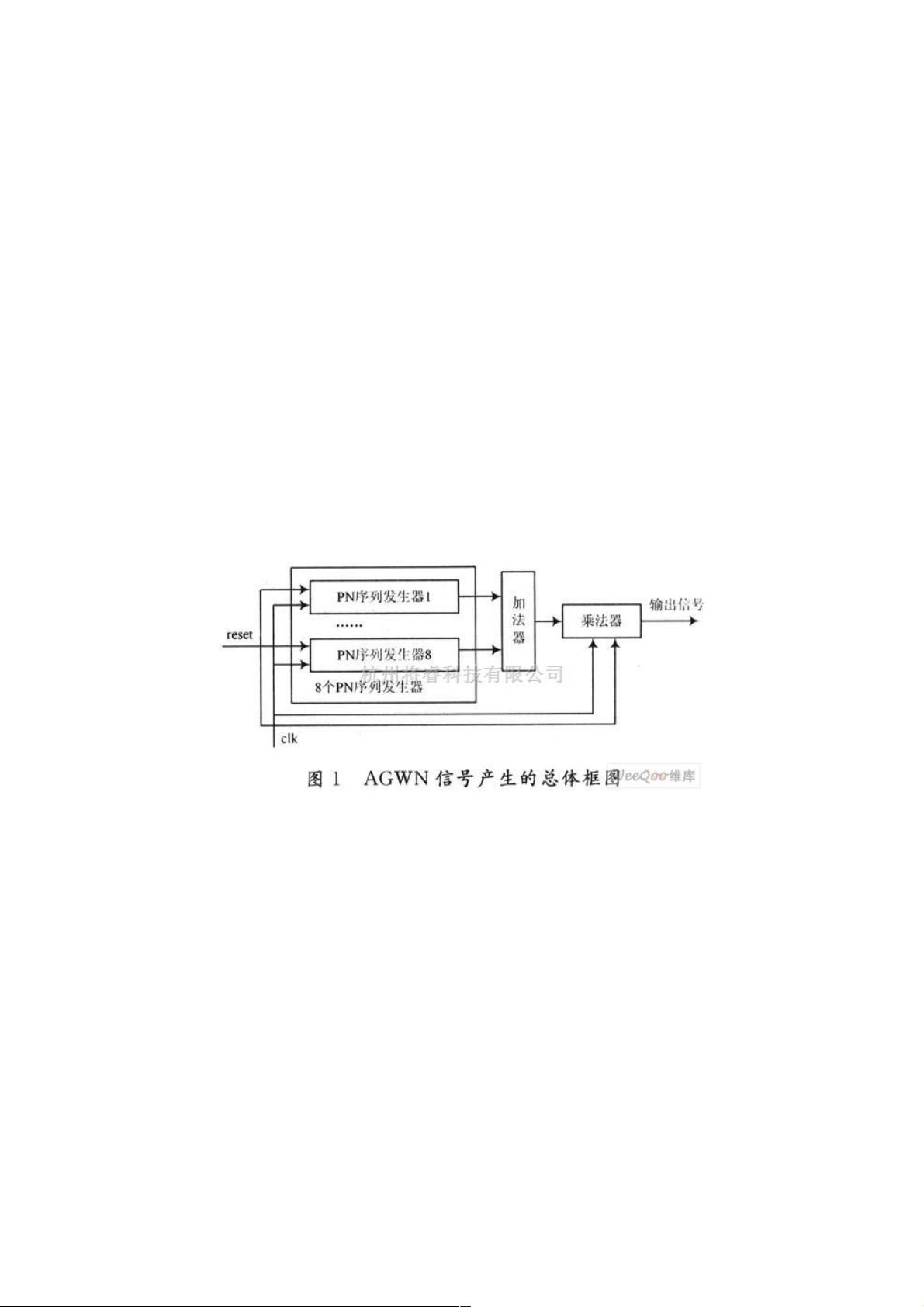

设计过程中,首先理解了AGWN的基本特性,它既满足白噪声的特征(功率密度函数在所有频率上恒定,表现为均匀分布),又满足高斯噪声的特性(概率密度函数符合高斯分布)。为了实现这种复杂的信号生成,设计者采用了自顶向下的设计策略,将整个AGWN信号生成过程分解为多个模块,包括白噪声生成、伪随机序列生成、叠加以及可变系数调整等步骤。

在FPGA平台上,设计者利用了8个独立且初始状态不同的线性反馈移位寄存器(LFSR)来生成8个独立的伪随机序列,每个序列都有实部和虚部,这些伪随机序列由于其不相关性,其功率谱密度符合白噪声特性。通过中心极限定理,将这8个信号相加以增强模拟高斯性。最终,通过调整一个可变系数,生成的信号可以精确地模拟AGWN的特性,并适应于数字通信系统的需求。

设计出的AGWN信号发生器不仅可以高效地生成数字形式的AGWN信号,简化信号产生流程,而且由于其灵活性和并行性,能够在FPGA中快速实现,对实时性和资源利用率有显著优势。这个设计方法对于测试通信系统的抗噪声性能、噪声抑制算法以及信号处理等方面具有实际应用价值。

本文介绍了一种在EDA/PLD领域中基于FPGA的AGWN信号生成器的设计实现,它展示了如何通过硬件描述语言Verilog,结合随机过程理论和数字信号处理技术,构建出能够模拟通信系统中复杂信道噪声的理想工具,为数字通信系统的性能评估和优化提供了强大支持。

点击了解资源详情

点击了解资源详情

点击了解资源详情

683 浏览量

124 浏览量

108 浏览量

188 浏览量

302 浏览量

205 浏览量

weixin_38595850

- 粉丝: 7

- 资源: 900

最新资源

- 上海大众供应商物流与采购过程分析规则

- ubs-for-uta-6324:适用于utaSpring2021的ubs系统adv sse 6324课程

- Open Source on the Xbox 360:xbox360 游戏机上的 UNIX/LINUX 和合法自制软件-开源

- 里科米达

- Sarkari Job-crx插件

- ShengSanYi-ArduinoEsp8266-master.zip

- domocracy:Domocracy 的开源工具

- 设施规划与物流分析PDF

- COMPENG-2DX4:该存储库保存了我的2021年冬季微处理器系统项目课程中所用的代码,在该课程中,我学习了如何对ARM MSP-EXP432微控制器进行编程。 我在各种外围设备(包括电机和键盘)上使用了ARM-Assembly,ARM-C和Python,所有这些都构成了构建LIDAR映射传感器的最终项目

- biningo

- project-flyer:我的克隆项目传单

- jquery.page分页控件02.zip

- 4EnRaya:我首先通过控制台在三个版本中连续玩四个,然后是摇摆,最后是在线

- ShopOnline.DotNetCore3:ShopOnline.DotNetCore3

- 图形化-班级成绩管理系统.zip

- CSCI370-Lab_04:异步任务