"基于BIST的NoC通信架构测试研究:解决SoC限制性问题及时钟同步挑战"。

版权申诉

100 浏览量

更新于2024-03-17

收藏 5.88MB PDF 举报

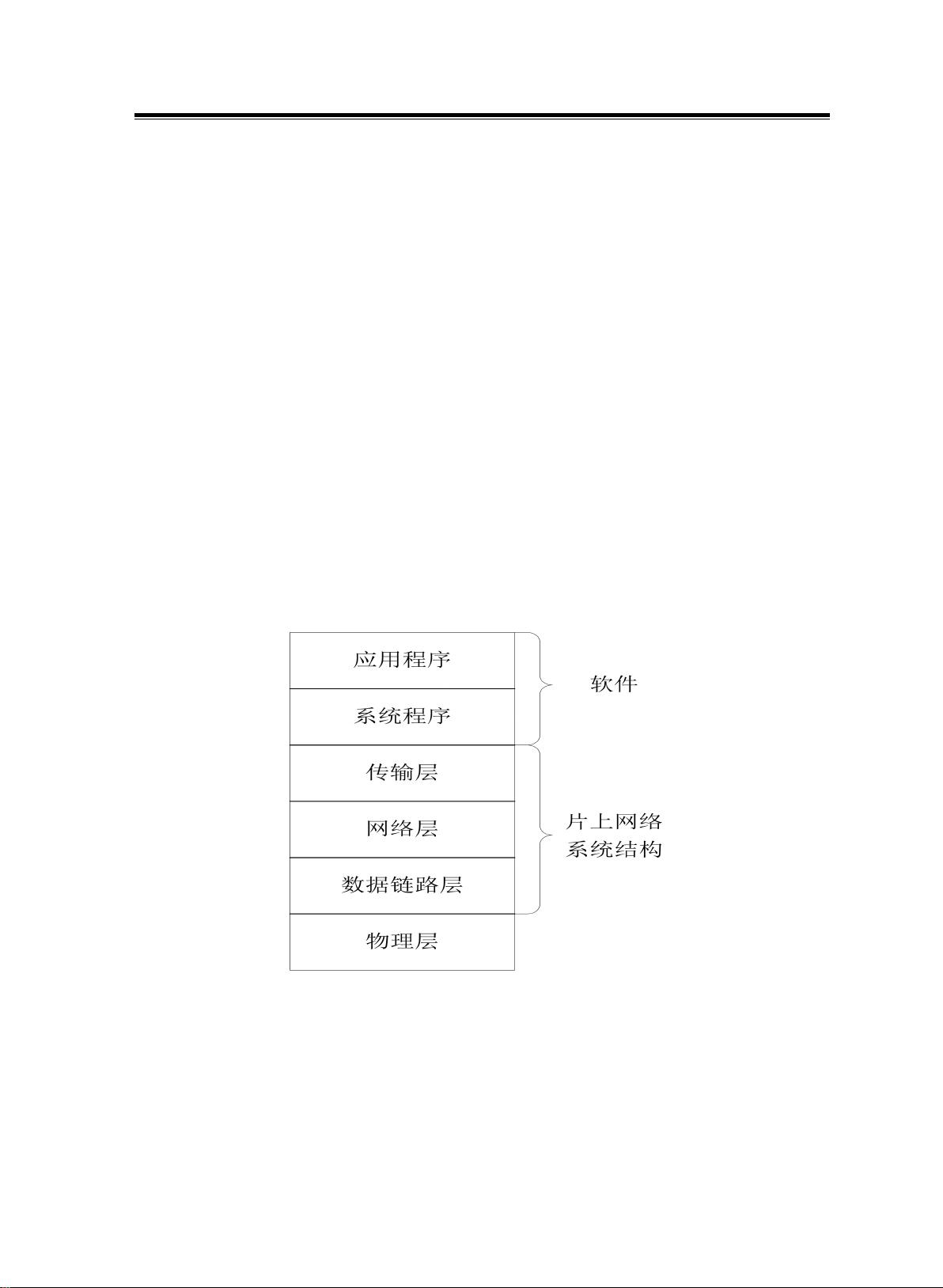

The research paper "Communication Architecture Testing of NoC System Based on BIST in Computer Backend" explores the challenges faced in System on Chip (SoC) design, including limited address space and the inability to support multiple user groups communicating simultaneously. To address these issues, the concept of Network-on-Chip (NoC) was introduced by the Royal Swedish Academy of Sciences, which utilizes packet switching technology instead of traditional bus communication.

The paper delves into the unique communication structure of NoC and investigates how Built-In Self-Test (BIST) can be utilized to test and optimize the communication architecture of NoC systems. By incorporating BIST into the design process, researchers aim to improve the reliability and efficiency of communication within SoCs, ultimately enhancing overall system performance.

Through a series of experiments and simulations, the researchers analyze the effectiveness of BIST in testing the communication architecture of NoC systems. They explore various methods for synchronization and clock management to ensure seamless communication between different components of the system. Additionally, the paper discusses the integration of BIST into the design flow of NoC systems and the potential benefits of utilizing this testing technique.

Overall, the research presented in the paper provides valuable insights into the testing and optimization of communication architectures in NoC systems using BIST. By addressing the challenges faced in SoC design, this work contributes to the advancement of computer backend technology and lays the foundation for further research in this field.

2021-07-13 上传

2021-07-13 上传

2022-09-14 上传

2021-07-26 上传

2019-07-22 上传

2021-08-11 上传

2021-07-26 上传

2022-09-23 上传

2021-07-26 上传

programmh

- 粉丝: 4

- 资源: 2162

最新资源

- Fisher Iris Setosa数据的主成分分析及可视化- Matlab实现

- 深入理解JavaScript类与面向对象编程

- Argspect-0.0.1版本Python包发布与使用说明

- OpenNetAdmin v09.07.15 PHP项目源码下载

- 掌握Node.js: 构建高性能Web服务器与应用程序

- Matlab矢量绘图工具:polarG函数使用详解

- 实现Vue.js中PDF文件的签名显示功能

- 开源项目PSPSolver:资源约束调度问题求解器库

- 探索vwru系统:大众的虚拟现实招聘平台

- 深入理解cJSON:案例与源文件解析

- 多边形扩展算法在MATLAB中的应用与实现

- 用React类组件创建迷你待办事项列表指南

- Python库setuptools-58.5.3助力高效开发

- fmfiles工具:在MATLAB中查找丢失文件并列出错误

- 老枪二级域名系统PHP源码简易版发布

- 探索DOSGUI开源库:C/C++图形界面开发新篇章