"FPGA数字锁相环设计及Verilog HDL基础"

版权申诉

7 浏览量

更新于2024-03-28

1

收藏 1.25MB DOCX 举报

本文主要介绍了基于FPGA的数字锁相环的设计。在第一章中,首先介绍了锁相环技术的发展及研究现状,指出锁相环在通信、导航、雷达等领域的重要性。接着阐述了本课题的研究意义,即通过FPGA设计数字锁相环,可以提高系统的性能和稳定性。最后明确了本课题的设计内容,即基于FPGA实现数字锁相环的功能。

在第二章中,重点介绍了FPGA的设计基础。首先讲解了硬件描述语言Verilog HDL的基本语法和应用,Verilog HDL是FPGA设计中常用的语言,能够描述数字逻辑电路的行为。然后详细介绍了FPGA的设计流程,包括设计需求分析、功能分解、模块设计、仿真验证、综合布局布线等步骤,这些步骤是FPGA设计的基本流程,确保设计的正确性和稳定性。

接着在第三章中,详细介绍了数字锁相环的原理和设计方案。数字锁相环是一种利用数字信号处理技术实现的锁相环系统,可以实现信号同步和频率合成的功能。通过分析数字锁相环的工作原理和基本结构,设计了适用于FPGA的数字锁相环方案,包括相位检测、频率控制、数字滤波等功能模块的设计。

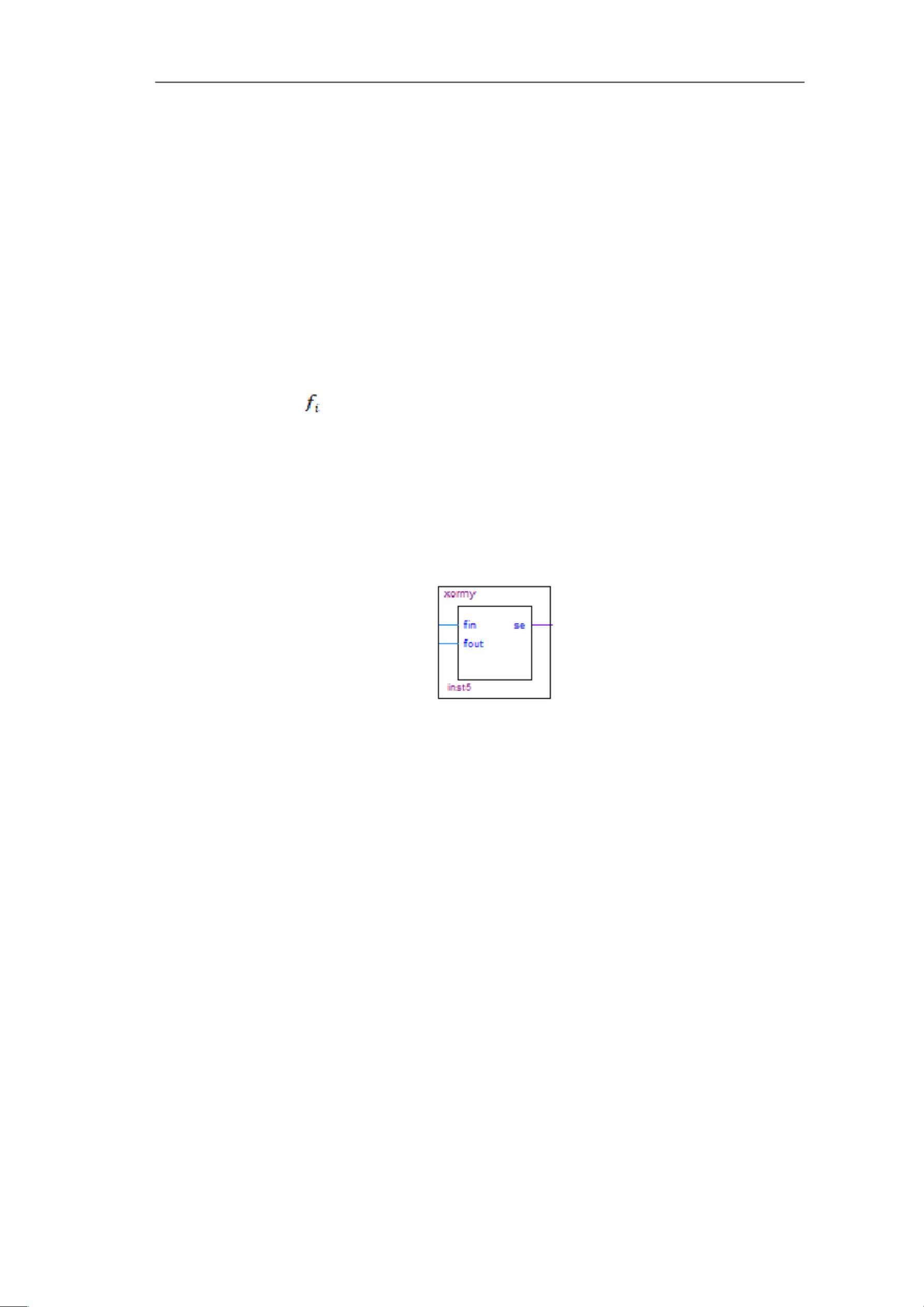

在第四章中,介绍了数字锁相环系统的FPGA实现。通过Verilog HDL语言实现了数字锁相环各个功能模块的设计,包括相位频率检测器、数字控制器、数字滤波器等。然后通过仿真验证和实际测试,验证了数字锁相环系统的功能和性能,确保了设计的正确性和稳定性。

最后在第五章中,总结了本文的研究工作。通过对基于FPGA的数字锁相环设计的详细介绍和实验验证,证明了数字锁相环在通信和导航等领域的重要性和应用前景。本文的研究为数字锁相环的设计和应用提供了一种有效的解决方案,同时也为FPGA在数字信号处理领域的应用提供了参考和借鉴。

综上所述,本文深入探讨了基于FPGA的数字锁相环的设计原理和实现方法,通过详细的设计方案和实验验证,证明了数字锁相环在通信和导航等领域的重要性和应用前景。同时也为FPGA在数字信号处理领域的应用提供了有效的参考和借鉴。希望本文的研究成果能够对相关领域的研究和工程应用有所帮助。

2022-11-01 上传

2022-07-10 上传

2021-09-15 上传

2021-05-30 上传

2024-10-13 上传

2022-06-20 上传