DDR2设计关键点:芯片选择与布线指南

需积分: 15 53 浏览量

更新于2024-09-14

收藏 488KB PDF 举报

DDR2设计是一项关键的硬件任务,它涉及到芯片的选择、管脚的配置、线路布局和信号处理等多个方面。本文主要关注DDR2 SDRAM的设计注意事项,特别是针对MT47H64M16HR-37E芯片的具体应用。

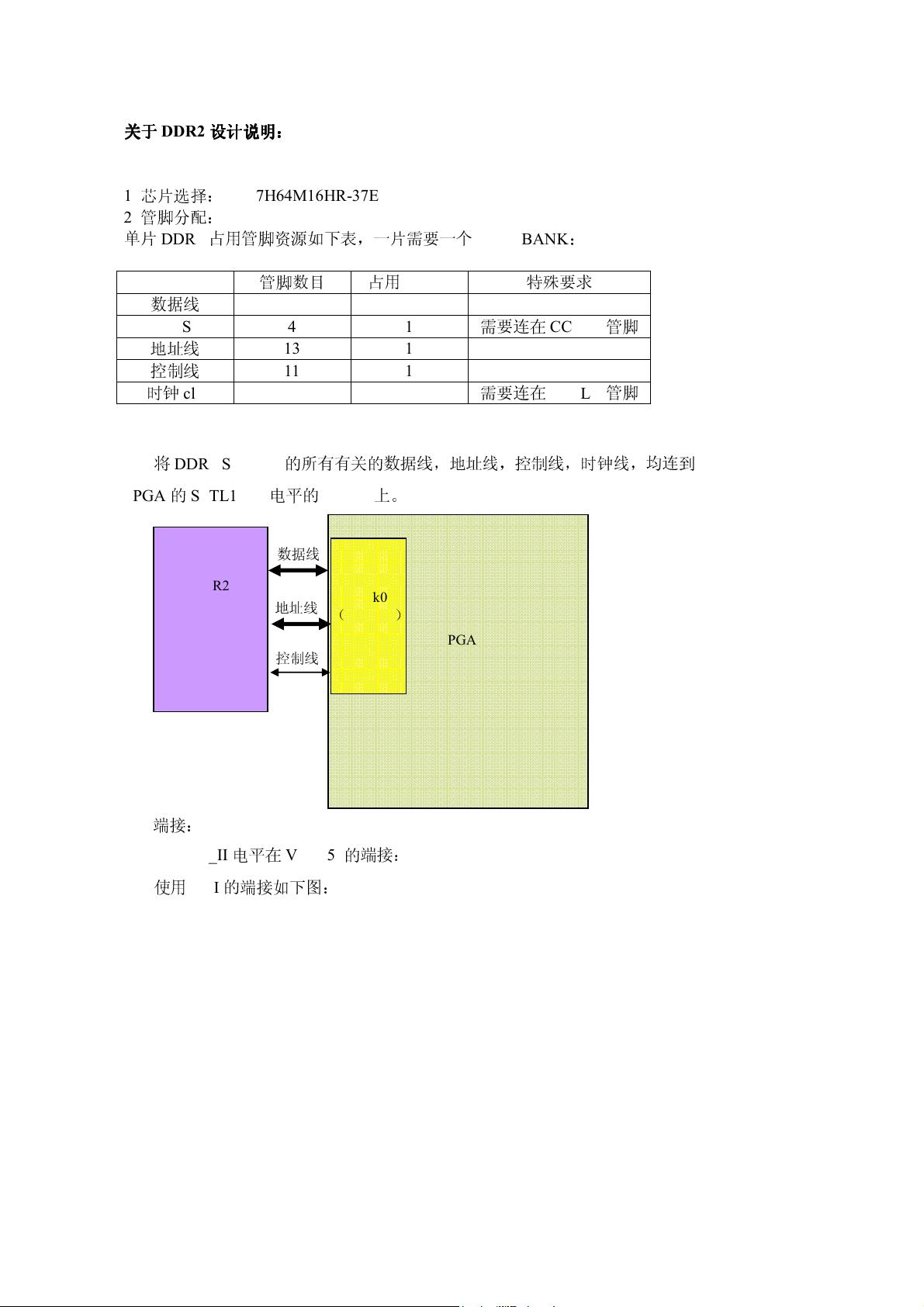

首先,芯片选择至关重要。MT47H64M16HR-37E是一个常用的DDR2内存芯片,其设计时需要确保单片DDR2占用一个FPGA BANK资源,并明确指出数据线、地址线、控制线和时钟线的具体配置。数据线包括DQ、DQS和DM,它们的操作基于时钟的双沿同步,因此在布线时需要遵循等长原则,DQ/DQS/DM线长应小于50mil,且组间长度差不超过1000mil。DQS信号与CK(时钟)之间的长度约束较为宽松,只要两者间的长度差别不大于1000mil即可。

在信号连接方面,DQS信号必须连接到IO_LxN_CC_LC指定的管脚上,确保正确的信号传输。对于时钟信号,由于它是FPGA输出给DDR2的,所以需要特别注意时钟线的等长要求,通常情况下,差分对的总长度要小于50mil,且两个时钟CK之间的间距不能少于100mil。此外,地址线和控制线也需要根据源同步原则进行适当调整,它们的长度可以比时钟线稍长。

供电部分,DDR2 SDRAM的工作电压为1.8V,这是设计过程中不可忽视的基本参数。电源设计需遵循制造商的推荐,确保稳定的电压和电流供应,以防止过电压或欠电压对内存性能造成影响。

在PCB布线顺序上,建议遵循数据线、地址线、控制线再到时钟线的顺序,同时要考虑到线路上不同信号类型的特性,如电阻值的设定,这对于信号完整性至关重要。整体来说,DDR2设计需要注意信号质量、线长匹配、电源管理以及管脚连接的精确性,这些都是保证系统稳定性和性能的关键要素。

DDR2设计中的关键点包括芯片选择、管脚分配、信号线路设计、电源管理以及PCB布局规则。每个环节都需要精心处理,以确保系统的高效运行和长期稳定性。在实际设计过程中,还需参考相关文档和标准,结合具体硬件平台进行细致的分析和优化。

2012-03-14 上传

点击了解资源详情

点击了解资源详情

2020-11-05 上传

2022-09-19 上传

2013-10-28 上传

2021-07-13 上传

2018-04-20 上传

qinxiongxu

- 粉丝: 71

- 资源: 14

最新资源

- NIST REFPROP问题反馈与解决方案存储库

- 掌握LeetCode习题的系统开源答案

- ctop:实现汉字按首字母拼音分类排序的PHP工具

- 微信小程序课程学习——投资融资类产品说明

- Matlab犯罪模拟器开发:探索《当蛮力失败》犯罪惩罚模型

- Java网上招聘系统实战项目源码及部署教程

- OneSky APIPHP5库:PHP5.1及以上版本的API集成

- 实时监控MySQL导入进度的bash脚本技巧

- 使用MATLAB开发交流电压脉冲生成控制系统

- ESP32安全OTA更新:原生API与WebSocket加密传输

- Sonic-Sharp: 基于《刺猬索尼克》的开源C#游戏引擎

- Java文章发布系统源码及部署教程

- CQUPT Python课程代码资源完整分享

- 易语言实现获取目录尺寸的Scripting.FileSystemObject对象方法

- Excel宾果卡生成器:自定义和打印多张卡片

- 使用HALCON实现图像二维码自动读取与解码