DDR2 Layout详解:关键注意事项与设计指南

本文主要关注于DDR2内存芯片的布局(Layout)指南,针对嵌入式系统设计者提供详细的技术参考。DDR、DDR2和DDR3是动态随机访问存储器(DRAM)技术的进化,其中DDR2在当前应用中占据主导地位,而DDR3正在逐步取代DDR2,它们之间的主要区别在于内部逻辑的“预取”技术。尽管数据传输速率理论上相同(例如,时钟频率为266MHz),但在实际应用中,要注意理解比特率(BitRate)的概念,它涉及到数据周期中的'0'与'1'组合。

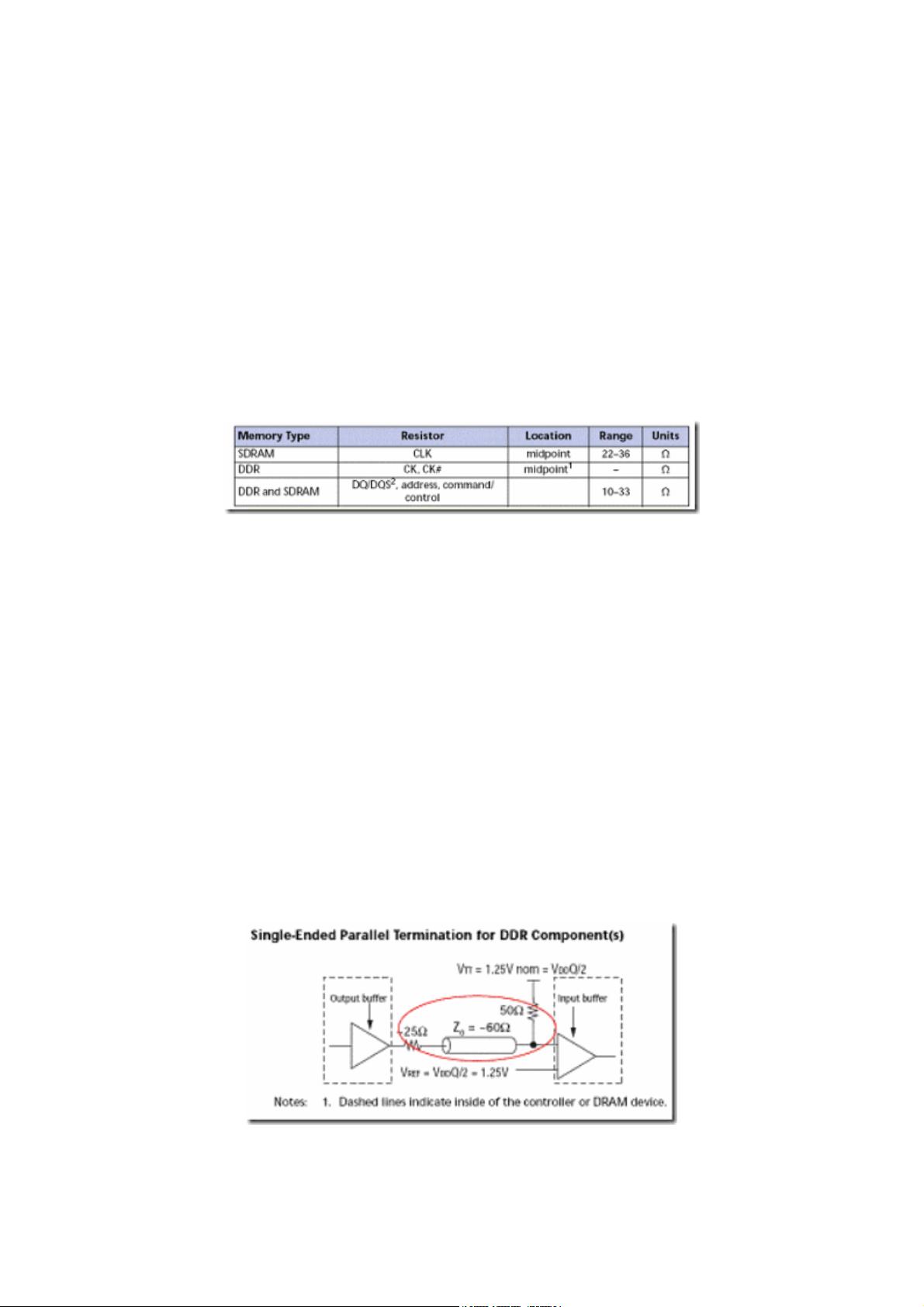

本文基于Micron和Freescale的设计指南,介绍了DDR2布局的关键要点,包括但不限于信号线的定义和管理。信号组分为数字信号组(DQ、DQS、DM,每个包含8个独立的通道)、地址信号组、命令信号组和控制信号组,以及时钟信号组。这些信号的正确布局对性能和稳定性至关重要。

在PCB设计方面,推荐使用6层电路板,以实现最佳的信号完整性,目标阻抗控制在50到60欧姆,同时考虑到印制电路板的厚度,建议选择1.5英寸。此外,文中还提到了地线的处理,如VSS(数字地)和VSSQ(信号地)的区别,以及VDD(内核供电)和VDDDQ(DQ和I/O供电)的等效性。

为了辅助理解,本文还引用了作者自己的文章编号lql-xxx,以及与DDR设计检查清单(DDR2 design checklist)的关联,以便设计者在实践中遵循DDR2设计原则。本文旨在帮助工程师们优化DDR2内存的布局,以确保系统性能和信号质量,从而在嵌入式系统设计中取得成功。

732 浏览量

1073 浏览量

106 浏览量

2014-08-05 上传

点击了解资源详情

点击了解资源详情

106 浏览量

点击了解资源详情

点击了解资源详情

heilangchuanshuo

- 粉丝: 0

- 资源: 2

最新资源

- 中国项目管理师培训讲义——费用管理

- SWF:一些用于处理SWF文件的python脚本

- 作品集:专为展示我的所有作品而创建的项目

- neural_network_projects:这是一些基本的神经网络

- STSensNet_Android:“ ST BLE StarNet” Android应用程序源代码-Android application source code

- SLIC-ImageSegmentation:基于SLIC图像分割算法实现一个比PS魔棒工具还方便的抠图工具

- yet-another-istanbul-mocha-no-coverage

- 四卡功能

- android 一个杀进程 程序分享,包含源代码-网络攻防文档类资源

- babel_pug_project:通过babel,pug,node,express进行Web服务器教育.....

- 爱普生7710 7720l免芯片固件刷rom附安装说明

- GenericInstsBenchmark

- AK_Lab2

- MADSourceCodes:“使用Android移动应用程序开发”课程源代码-Android application source code

- themeweaver:使用设计标记在浏览器中创建kick-ass IDE主题!

- oo-way-getonboard中的战舰:GitHub Classroom创建的oo-way-getonboard中的战舰