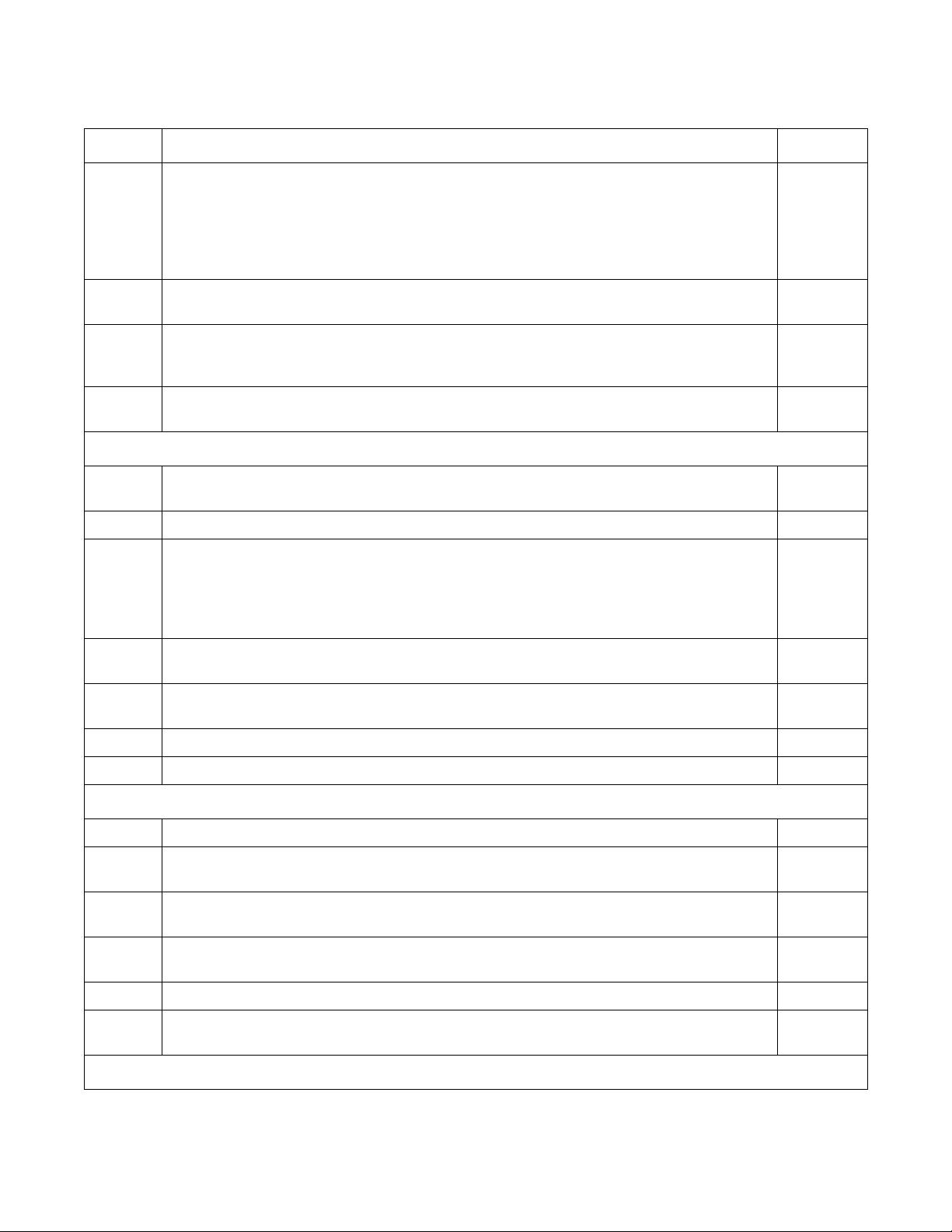

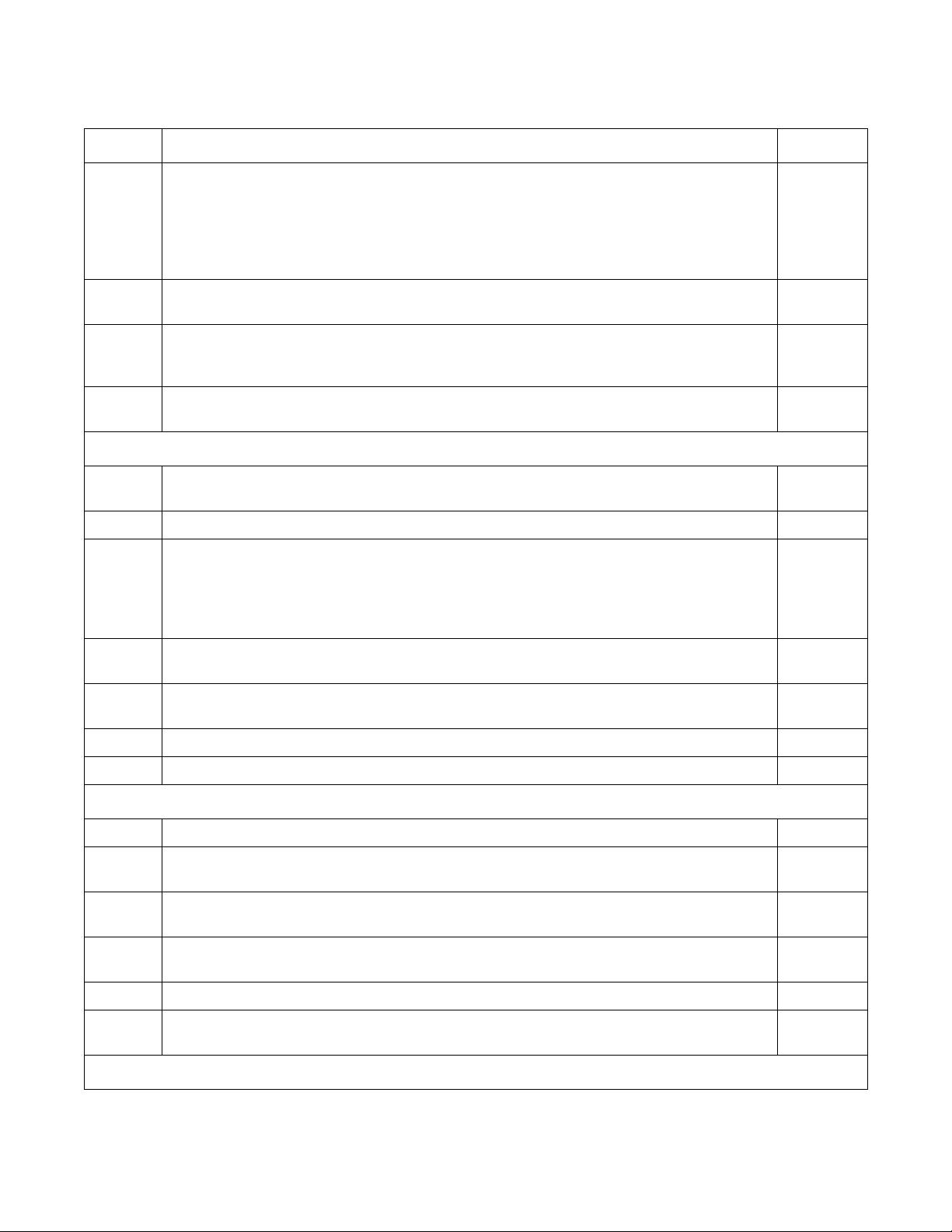

7. For address and command signals, the Micron compensation cap scheme is another optional

termination method for improving eye apertures for a heavily loaded system (> 18 memory chips).

For details on this termination scheme refer to DDR533 Memory Design for Two-DIMM Unbuffered

Systems, located on Micron’s web site. For lightly and medium loaded memory subsystems (4–18

chips), the compensation cap method is not as beneficial.

If used, are the C

COMP

capacitors placed within 0.5 inch of the first memory bank?

8. Is the differential terminator present on the clock lines for discrete memory populations? (DIMM

modules contain this terminator.) Nominal range => 100-120 Ω.

9. Recommend that an optional 5pF cap be placed across each clock diff pair. If DIMM modules are

used, the cap should be placed as closely as possible to the DIMM connector. If discrete devices

are used, the cap should be placed as closely as possible to the discrete devices.

10. Recommendation—Place 0-Ω resistors on the DDR2 clock lines (near the driver). Such flexibility

allows the clock lengths to be extended (if needed) during the prototyping phase.

V

TT

Related Items

11. Has the worst case current for the V

TT

plane been calculated based on the design termination

scheme? See Section 2, “Termination Dissipation”.

12. Can the V

TT

regulator support the steady state and transient current needs of the design?

13. Has the V

TT

island been properly decoupled with high frequency decoupling? At least 1 low ESL

cap, or 2 standard decoupling caps for each 4-pack resistor network (or every 4 discrete resistors)

should be used. In addition, at least one 4.7-μF cap should be at each end of the V

TT

island.

Note: This recommendation is based on a top-layer V

TT

surface island (lower inductance). If an

internal split is used, more capacitors may be needed to handle the transient current demands.

14. Has the V

TT

island been properly decoupled with bulk decoupling? At least 1 bulk cap (100–220 μF)

capacitor should be at each end of the island.

15. Has the V

TT

island been placed at the end of the memory channel and as closely as possible to the

last memory bank? Is the V

TT

regulator placed in close proximity to the island?

16. Is a wide surface trace (~150 mils) used for the V

TT

island trace?

17. If a sense pin is present on the V

TT

regulator, is it attached in the middle of the island?

V

REF

18. Is V

REF

routed with a wide trace? (Minimum of 20–25 mil recommended.)

19. Is V

REF

isolated from noisy aggressors? In addition, maintain at least a 20–25 mil clearance from

V

REF

to other traces. If possible, isolate V

REF

with adjacent ground traces.

20. Is V

REF

properly decoupled? Specifically, decouple the source and each destination pin with 0.1uf

caps.

21. Does the V

REF

source track variations in VDDQ, temperature, and noise as required by the JEDEC

specification?

22. Does the V

REF

source supply the minimal current required by the system (memories + processor)?

23. If a resistor divider network is used to generate V

REF

, are both resistors the same value and 1%

tolerance?

Routing

Table 1. DDR2 Designer’s Checklist (continued)

Item Description Yes/No