EDA技术应用:8路抢答器设计与实现

"基于EDA的8路抢答器设计涵盖了EDA技术的基本介绍、设计目标以及具体实现要求。项目使用EDA工具,如Quartus II,结合硬件描述语言VHDL,来实现一个功能完整的八路抢答器系统,旨在提升对FPGA/CPLD的理解与应用技能。"

在本项目中,EDA(Electronic Design Automation)技术扮演了核心角色。EDA技术是一种利用计算机辅助设计的方法,它允许设计者借助专用的软件平台,如Quartus II,用硬件描述语言(HDL,如VHDL)编写设计文件。该技术能够自动化地完成逻辑编译、优化、布局、布线等一系列复杂的电路设计任务,显著提高了设计效率并降低了设计错误的可能性。

20世纪90年代以来,随着可编程逻辑器件(如CPLD和FPGA)的广泛应用,EDA技术得到了快速发展。这些器件允许硬件结构和工作方式的动态配置,为数字系统的创新设计提供了无限可能。EDA技术不仅简化了设计流程,还使得非专业硬件工程师也能进行复杂的电路设计。

八路抢答器的设计目标是学习和熟练掌握ALTERA公司的FPGA/CPLD器件特性,以及如何运用MAX+plus II/Quartus II这样的EDA软件进行设计。设计者需要通过VHDL硬件描述语言来定义抢答器的功能,包括八路输入、抢答逻辑、编号显示、成功指示和复位功能。这要求设计者不仅要有扎实的数字电路基础,还需要理解可编程逻辑器件的工作原理。

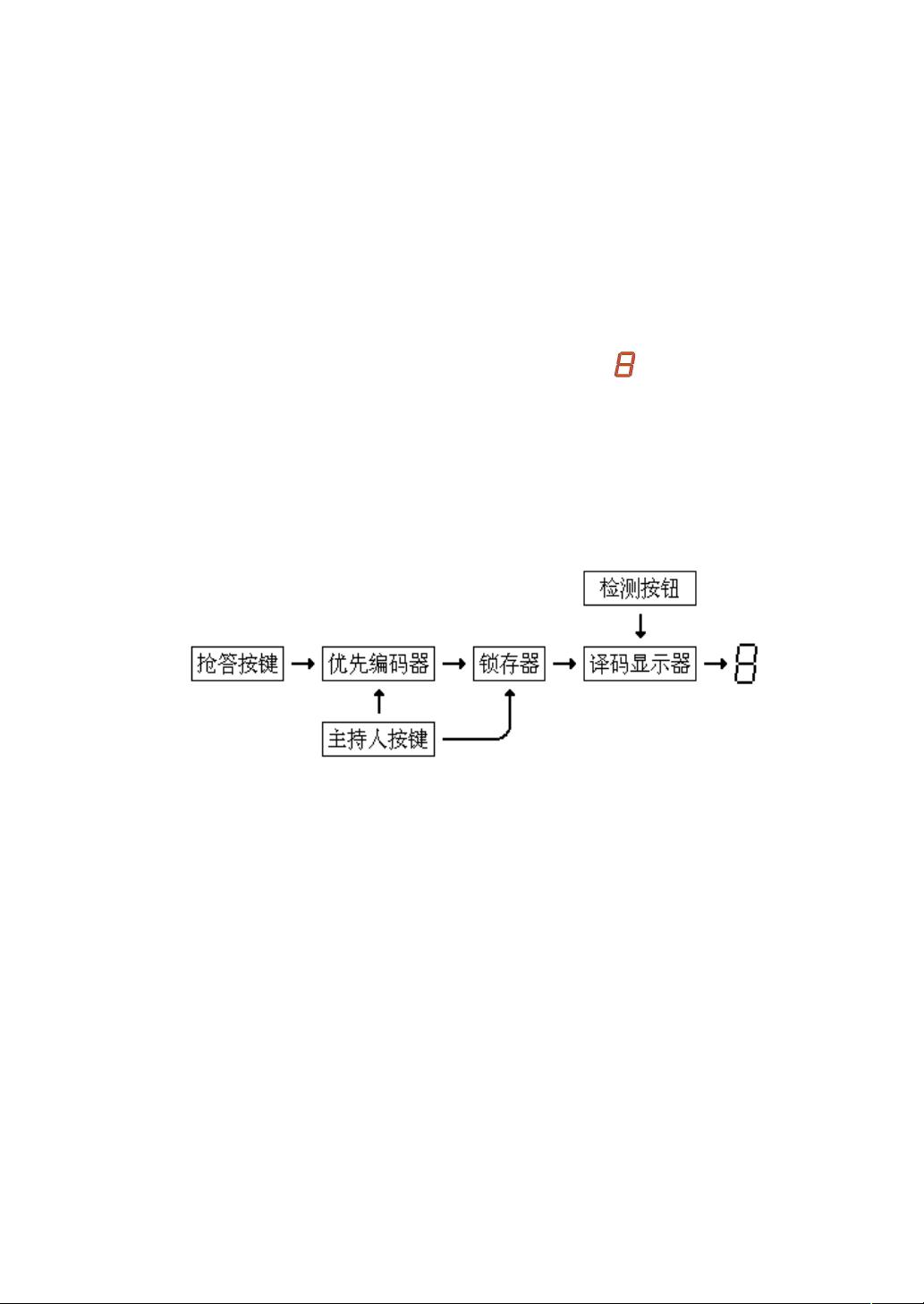

具体设计要求中,八路抢答器必须能在选定的器件内部实现所有功能。抢答逻辑设计需要确保公平性,一旦有选手按下抢答按钮,其他选手将被锁定无法再抢答。同时,系统需要能显示抢答成功的选手编号,提供抢答成功指示,并在抢答完成后能够自动复位,准备下一轮抢答。

这个基于EDA的8路抢答器项目是一个实践性强、理论与实践相结合的优秀学习案例,旨在通过实际操作提升设计者在数字电路设计和EDA工具应用方面的技能。通过该项目,学生不仅能深入理解FPGA/CPLD的工作机制,还能熟悉VHDL编程,以及掌握使用EDA工具进行复杂系统设计的方法。

683 浏览量

157 浏览量

271 浏览量

220 浏览量

119 浏览量

192 浏览量

没事偷着乐哈

- 粉丝: 0

- 资源: 1

最新资源

- mediacapture-screen-share:媒体捕获屏幕捕获规范

- mi-kasa-app

- nuka:可以开发的运营商的预配工具

- riscv-对RISC-V处理器的低级别访问-Rust开发

- My_Sublime_Text

- mybatis中文文档.rar

- firefox35+selenium自动化开发

- A.I.ware:Oware在线游戏,人类可以与机器人对战

- yelpcamp

- numberPool

- 行业文档-设计装置-面部识别早教机.zip

- rust-portaudio-PortAudio绑定-Rust开发

- 上课课件-2021版C语言 -【上课课件-2021版C语言 -【

- 纯css3黑色发光分享按钮特效

- todo_app

- birthdayHomeApp:在家中处理Bottega应用程序