异构多核SoC芯片:边界控制下的安全硬件架构与性能优化

需积分: 10 21 浏览量

更新于2024-09-01

收藏 347KB PDF 举报

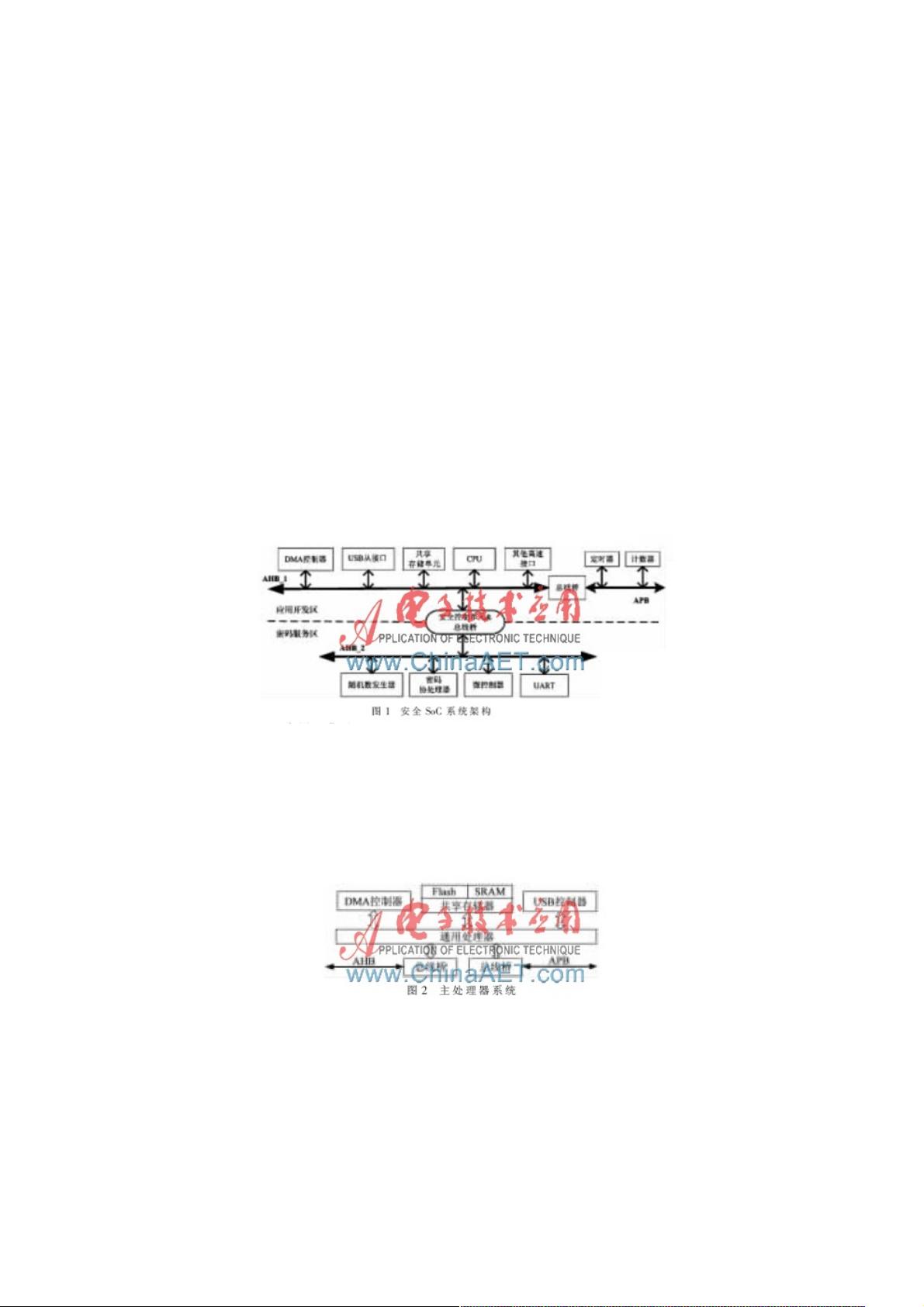

本文主要探讨的是"基于边界控制的安全SoC芯片硬件结构设计"。针对大规模数据处理和信息安全的需求,设计团队采用异构多核架构,结合通用处理器和专用密码协处理器,构建一款高性能且安全的SoC芯片。在系统设计中,他们深入分析了高性能SoC的基本结构和安全挑战,着重考虑了如何融合安全硬件结构和边界控制理念。

文章的核心在于提出了一个安全策略,即在SoC芯片中划分出密码服务区和应用开发区,两个区域之间通过专用安全控制单元进行硬件隔离。这个控制单元是通过真值表方法精心设计的,能够有效地防止应用开发区未经授权访问密码服务区,从而保护芯片免受恶意攻击,同时确保数据处理过程中的延迟最小化。

在多核SoC架构中,通用RISC处理器负责基础的数据流管理和数据分配,而专用的密码协处理器则专注于复杂的加密和解密任务。两者通过高效的多层系统总线进行通信,共享存储器缓存用于数据交换。应用开发区作为用户开发和接口区域,连接各种通信接口,由主处理器系统进行管理,它不仅负责设备管理、通信管理和控制任务,还负责应用程序的调度和分区,是整个SoC系统的核心控制部分。

本文的研究意义在于,通过硬件层面的安全设计,解决了传统软件安全方法在嵌入式环境中资源受限和复杂性增加的问题。这种设计不仅提升了系统的安全性,还保持了良好的性能和较低的功耗,对于处理计算密集型任务和应对信息安全挑战具有重要意义。通过采用EDA工具进行仿真实验,验证了所设计的安全控制单元的有效性和性能优化,为安全SoC芯片的实际应用提供了理论支持和实践指导。

2021-07-26 上传

2021-07-26 上传

2020-10-18 上传

2009-05-25 上传

2009-08-19 上传

2021-07-26 上传

2021-07-26 上传

2021-07-26 上传

2020-11-12 上传

weixin_38693589

- 粉丝: 5

- 资源: 928

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍