SerDes架构与应用解析

"SerDes架构与应用"

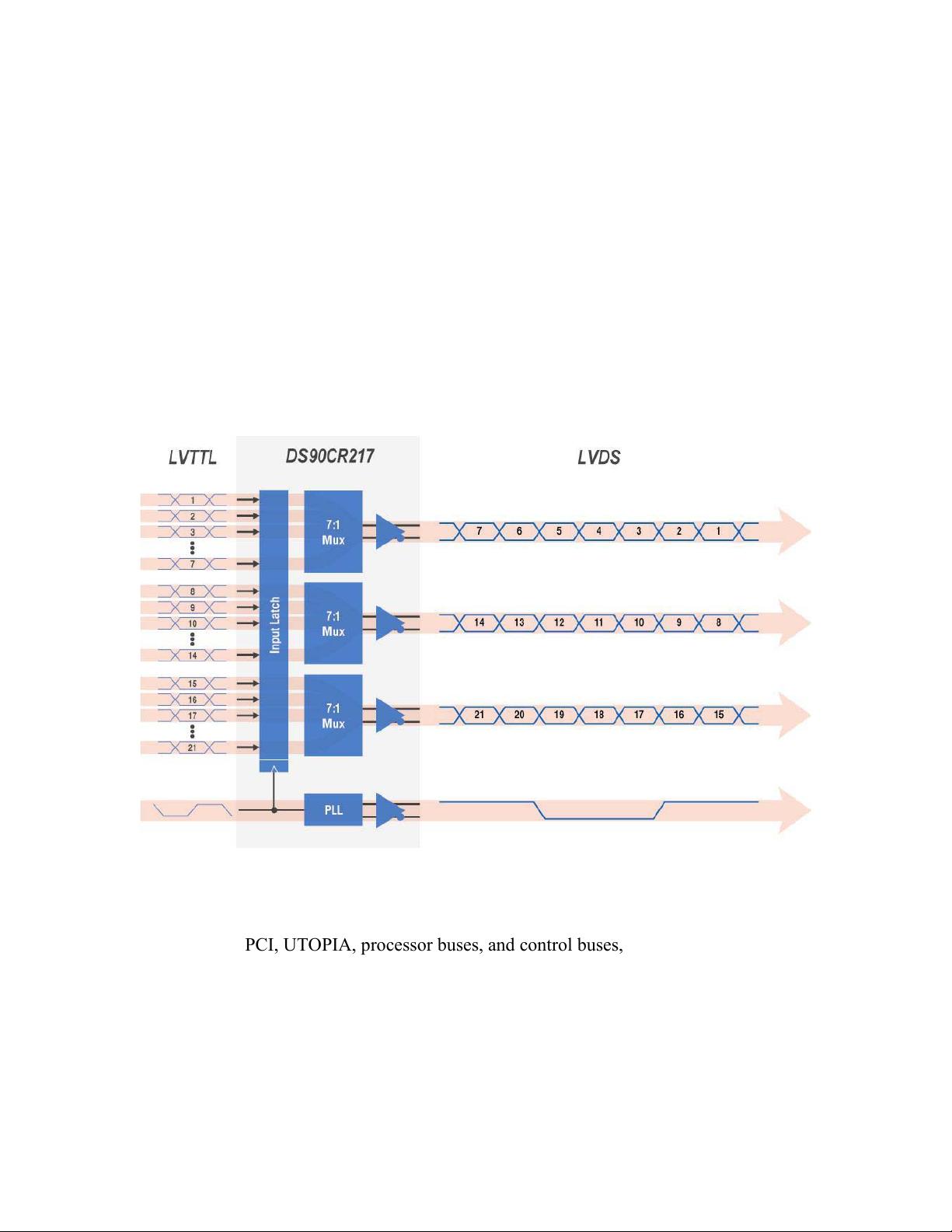

SerDes(Serializer/Derializer,串行器/解串行器)是现代高速通信系统中的关键组件,它负责在并行数据和串行数据之间进行转换,从而实现高速数据传输。本文主要探讨了SerDes的结构和应用场景,以及其对系统设计的影响。

首先,SerDes的硬件组成通常包括以下几个部分:

1. **串行器(Serializer)**:它将并行数据流转换为高速串行信号。这一过程涉及到数据编码,以提高信号质量和抗干扰能力。例如,8b/10b编码就是一种常见的编码方式,它将8位并行数据转换为10位串行数据,通过增加冗余来确保数据的完整性。

2. **解串行器(Deserializer)**:接收串行输入信号,并将其恢复为原始的并行数据流。解串行器需要正确地同步和解码输入信号,同时处理时钟恢复和均衡等任务,以确保数据的准确无误。

3. **时钟恢复电路**:在串行数据中提取时钟信息,这是解串行过程的关键步骤,因为串行数据中没有明确的时钟信号。

4. **前向错误校正(Forward Error Correction, FEC)**:用于检测和纠正传输过程中可能出现的错误,提高数据传输的可靠性。

5. **均衡器**:补偿传输媒介引起的信号失真,保持信号质量。

6. **接收器和发射器**:负责信号的放大、整形和驱动,以适应不同的传输介质。

SerDes有四种主要的架构类型:

1. **并行时钟SerDes**:这种架构依赖于一个共同的时钟源来同步发送端和接收端,适用于时钟精度要求高的环境。

2. **8b/10b SerDes**:通过在数据中嵌入特定的编码规则,提供数据完整性检查和时钟恢复功能。

3. **嵌入式时钟位(Start-Stop Bit)SerDes**:在数据序列中插入时钟信息,使得接收端可以解码数据并恢复时钟。

4. **位交织(Bit Interleaving)SerDes**:通过将数据位交错传输,可以在多个通道上分散信号失真,提高系统的整体带宽和容错能力。

这些不同架构的选择取决于具体的应用需求,如传输距离、带宽、功耗、成本和协议兼容性等因素。例如,8b/10b SerDes常用于PCIe和SAS等接口,而位交织SerDes则常见于光纤通信和数据中心互联。

系统设计师在选择SerDes时,需要考虑的参数包括系统拓扑、协议开销、数据格式和流量控制、延迟、时钟和定时要求,以及是否需要额外的缓冲和逻辑。这些因素直接影响到系统的性能、效率和成本。例如,更高的数据速率可能意味着更大的功耗,而更复杂的SerDes架构可能需要更多的系统资源来支持。

Dave Lewis的文章深入探讨了这四种SerDes架构的工作原理,对比了它们之间的差异,并展示了每种架构在当前广泛应用中的适应性。通过理解这些基础,系统设计师可以更好地优化他们的设计,满足不断增长的高速数据传输需求。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2019-01-23 上传

2013-03-08 上传

2022-07-15 上传

2021-09-11 上传

2022-07-14 上传

2023-08-03 上传

qingjiegong123

- 粉丝: 0

- 资源: 5

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率