CPLD在级联多电平变频器脉冲发生器设计中的应用

26 浏览量

更新于2024-08-31

收藏 212KB PDF 举报

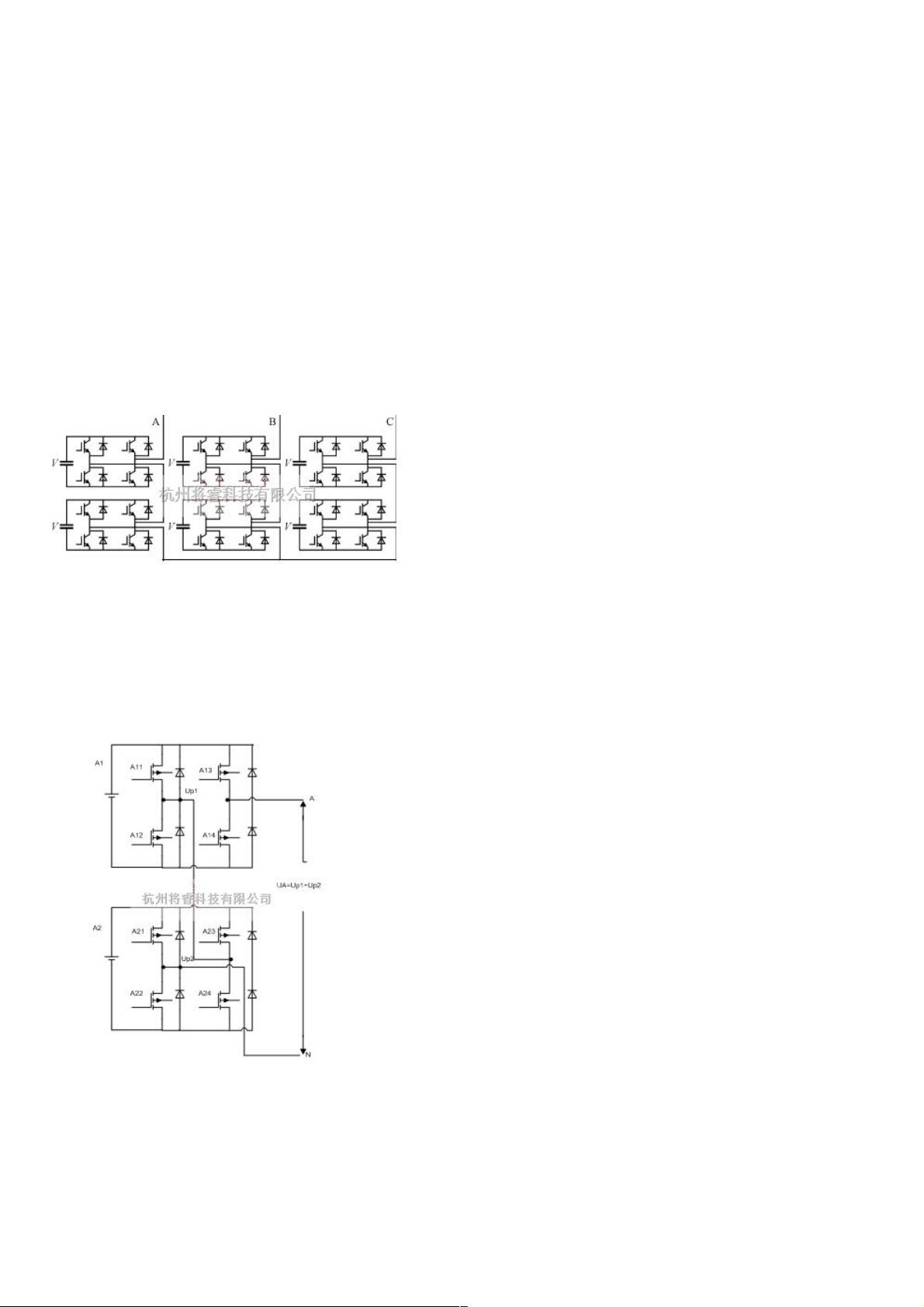

"本文主要探讨了在EDA/PLD(电子设计自动化/可编程逻辑器件)环境下,如何设计一种基于CPLD(复杂可编程逻辑器件)的级联型多电平变频器脉冲发生器,特别是针对三相五电平变频器的结构和工作原理进行了详细阐述。"

在电力电子领域,级联型多电平变频器因其独特优势受到广泛关注,尤其适用于中压大功率应用。常见的多电平变换器拓扑结构包括二极管箝位型、飞跨电容型和级联型。级联型变频器的优点在于无须使用箝位二极管和电容,简化了封装,同时解决了电容电压平衡的问题。本文重点介绍了级联型多电平变频器的脉冲发生器设计,利用CPLD技术实现高效能的PWM控制。

载波移相SPWM技术是PWM脉冲生成的关键,其原理是保持调制波频率和载波频率恒定,通过改变载波相位来生成SPWM信号。这种技术通过调整载波相位,可以产生不同相位的SPWM信号并进行线性组合,有效消除谐波并提高输出功率质量。例如,在三相五电平变频器中,每个相位需要两个单元,因此载波之间相差90度,以达到理想的谐波消除效果。

CPLD在三相五电平变频器的PWM脉冲发生器设计中起到核心作用。由于三相五电平变频器需要24路PWM脉冲,而单个DSP只能提供12路,因此采用了CPLD来扩展输出,满足更多通道的需求。CPLD内部的可编程逻辑可以根据预设的算法生成相应的PWM脉冲序列,确保各个开关器件的精确控制,进而实现多电平电压的平稳转换。

在实际应用中,CPLD可以通过编程实现灵活的控制策略,适应不同的运行条件和负载需求。其高速处理能力和高密度逻辑集成使得脉冲发生器设计更具效率和可靠性。此外,CPLD还允许动态调整PWM参数,如占空比和频率,以优化系统性能和降低谐波含量。

总结来说,基于CPLD的级联型多电平变频器脉冲发生器设计结合了载波移相SPWM技术的优势,实现了高效、低谐波的多电平电压变换。这种方法在电力电子领域中具有重要的理论价值和实践意义,尤其对于大型工业应用和清洁能源系统,提供了更加先进和优化的解决方案。

2020-11-08 上传

2020-12-10 上传

2020-11-09 上传

2020-11-07 上传

2020-12-06 上传

2020-11-03 上传

2020-12-10 上传

2020-11-09 上传

2020-12-13 上传

weixin_38670318

- 粉丝: 6

- 资源: 919

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析