SR锁存器详解与应用

"该资源是清华大学的一份关于SR锁存器的课件,主要涵盖了SR锁存器的工作原理、波形分析以及其构建方法。"

SR锁存器是一种基本的数字逻辑电路,常用于数据存储和状态保持。它由两个输入(S,Set,置位)和(R,Reset,复位)以及两个互补输出(Q,Q非)组成。在数字电子技术中,SR锁存器是构建更复杂逻辑电路的基础组件。

1. 基本SR锁存器的工作原理:

- 当S=0且R=0时,无论Qn的初态如何,输出Q和Q非将保持其当前状态,即锁存器的输出不会改变,这个状态称为“保持”或“不允许”状态。

- 如果S=1且R=0,锁存器会置1,即Qn+1=1,无论Qn的初始状态如何。

- 当S=0且R=1时,锁存器会置0,即Qn+1=0,同样不受Qn的影响。

- 然而,如果S和R同时为1(S=1,R=1),这将导致“竞争-冒险”情况,也称为“禁止”或“不允许”状态,此时输出Q和Q非可能处于不确定状态,因为两个输入同时激活会导致电路无法确定其输出,这是必须避免的约束条件。

2. SR锁存器的工作波形:

- 波形图通常描绘了S和R输入信号的变化以及相应的Q和Q非输出变化。在置1和置0的过程中,Q和Q非的跳变是在S或R信号上升沿发生。

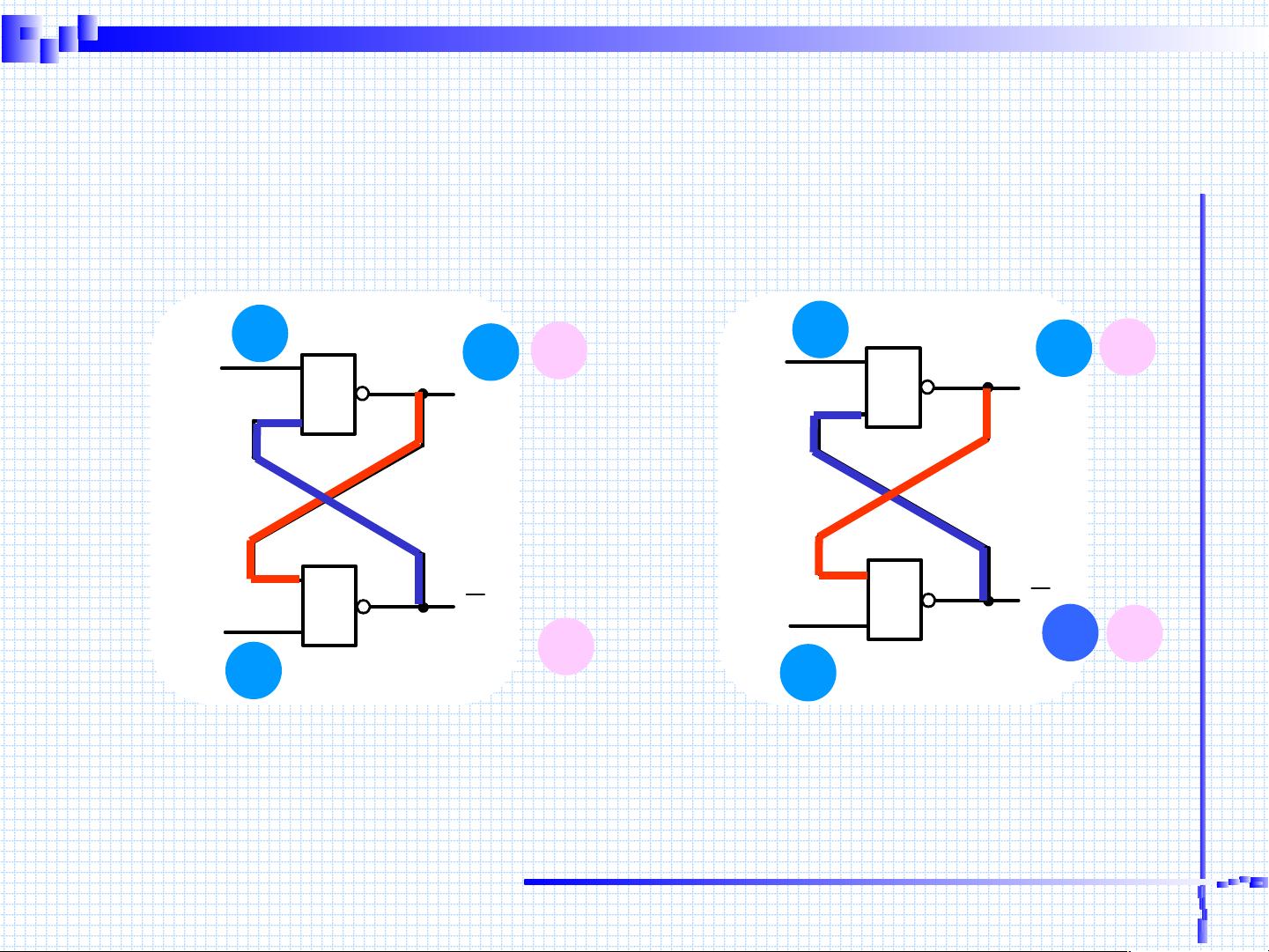

3. 与非门构成的基本SR锁存器:

- SR锁存器可以由四个与非门(NAND门)组成,其中每个输入端连接到一个与非门的输入,并且两个与非门的输出互相连接形成另一个与非门的输入,从而形成一个自互锁的结构。

- 国标逻辑符号表示了这种电路的连接方式,S和R作为控制输入,Q和Q非作为输出。

在实际应用中,SR锁存器经常与其他逻辑门或触发器结合,以构建更复杂的电路,如D锁存器、JK触发器等。需要注意的是,为了防止出现不确定状态,设计时必须确保在任何时刻S+R不等于0,即S和R不能同时为1。了解和掌握SR锁存器的工作原理及其限制对于理解和设计数字系统至关重要。

2023-10-24 上传

2023-11-28 上传

2023-11-28 上传

2023-05-05 上传

2023-07-27 上传

2024-10-31 上传

shi0615

- 粉丝: 5

- 资源: 8

最新资源

- Mathematics for Computer Graphics

- Tomcat 安装配置手册

- web课件第九章 ASP.NET的XML编程

- Java Struts教程

- 基于PLC的步进电机控制系统及其在火车轴温检测系统中的应用.pdf

- Eclipse中文教程

- 基于TCPIP的局域网多用户通信

- oracle动态过程执行

- WEB SERVICE

- 嵌入式Linux驱动开发实例分析

- linux c 编程.pdf

- 1_必读_高质量C++编程指南(林锐博士).pdf

- c语言指针经验总结.pdf

- kr.ac.jbnu.ssel.misrac:OpenMRC

- ogov-importer:阿根廷国会法案进口商

- 大数据导论PPT和期末复习笔记