Altera FPGA时序分析详述:TimeQuest入门与实践指南

需积分: 9 159 浏览量

更新于2024-07-21

收藏 3.8MB PDF 举报

Altera FPGA 时间quest分析是针对Altera公司FPGA(Field-Programmable Gate Array)设计者的重要工具,它在FPGA开发过程中扮演了关键角色,用于确保设计的时序性能满足系统需求。时间quest,即TimeQuest,是一个功能强大的工具,用于进行高级综合后的时间和面积分析,包括延迟、功耗和时钟树分析等。

文档详细介绍了TimeQuest用户指南的第1.1版,发布日期为2010年12月9日,作者Ryan Scoville是一位经验丰富的设计者,他在帮助他人解决时间quest相关问题的过程中,意识到需要一个集中整理的资源来分享他的学习心得。这份文档旨在成为一个一站式学习资料,尽管目前仍有一些部分缺失,但核心内容已经相当全面,足以满足大部分用户的日常使用需求。

文档建议读者:

1. 使用书签功能:为了更有效地导航,用户应利用文档中的书签标记重要的知识点,因为许多示例可能需要前后关联的内容。虽然文档中已经添加了超链接,但书签可以帮助用户快速定位到相关章节。

2. 开始阅读“入门”部分:这个部分包含了时间quest的基本概念和设置步骤,以及如何开始一个项目分析。对于初次接触TimeQuest的用户来说,这是了解工具的基础。

文档深入探讨了以下关键知识点:

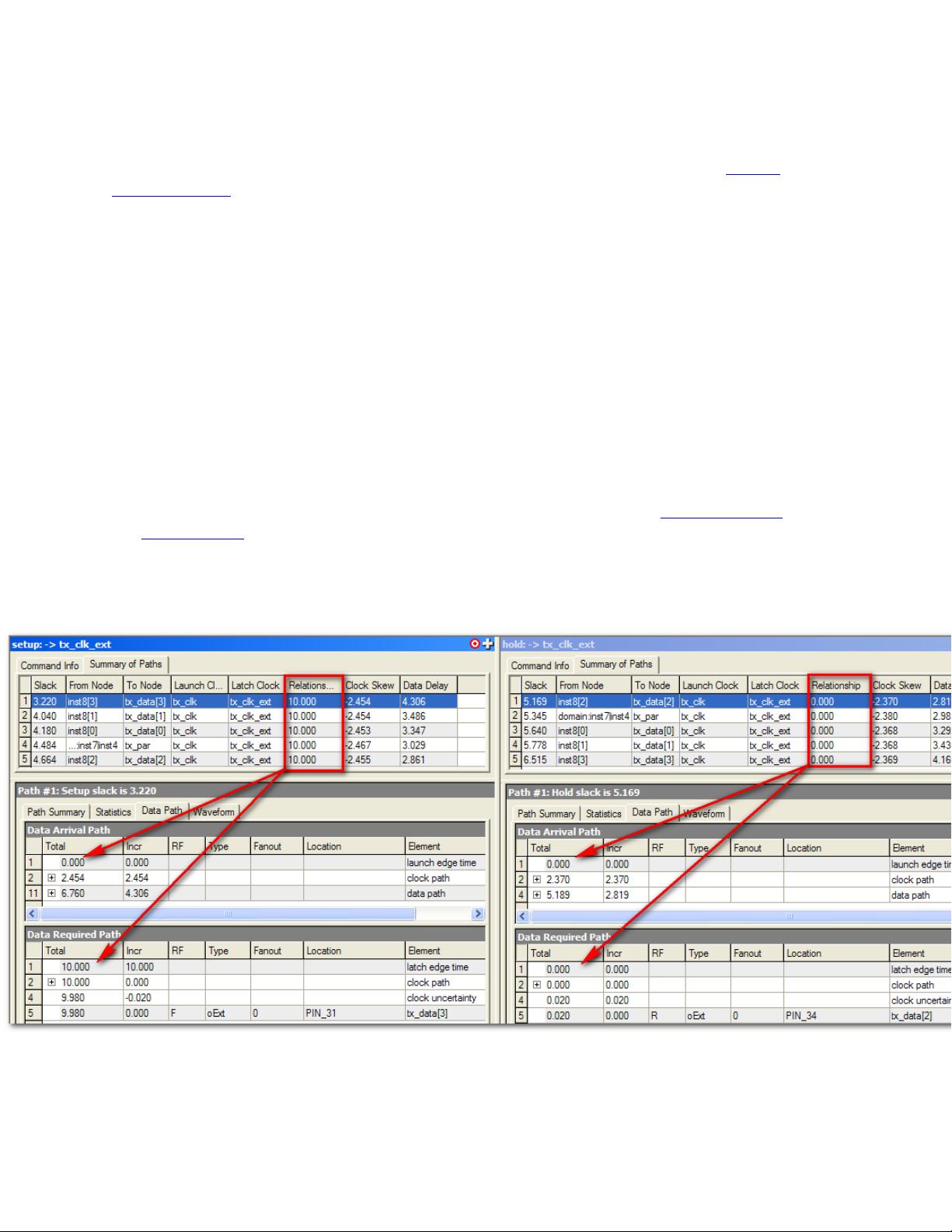

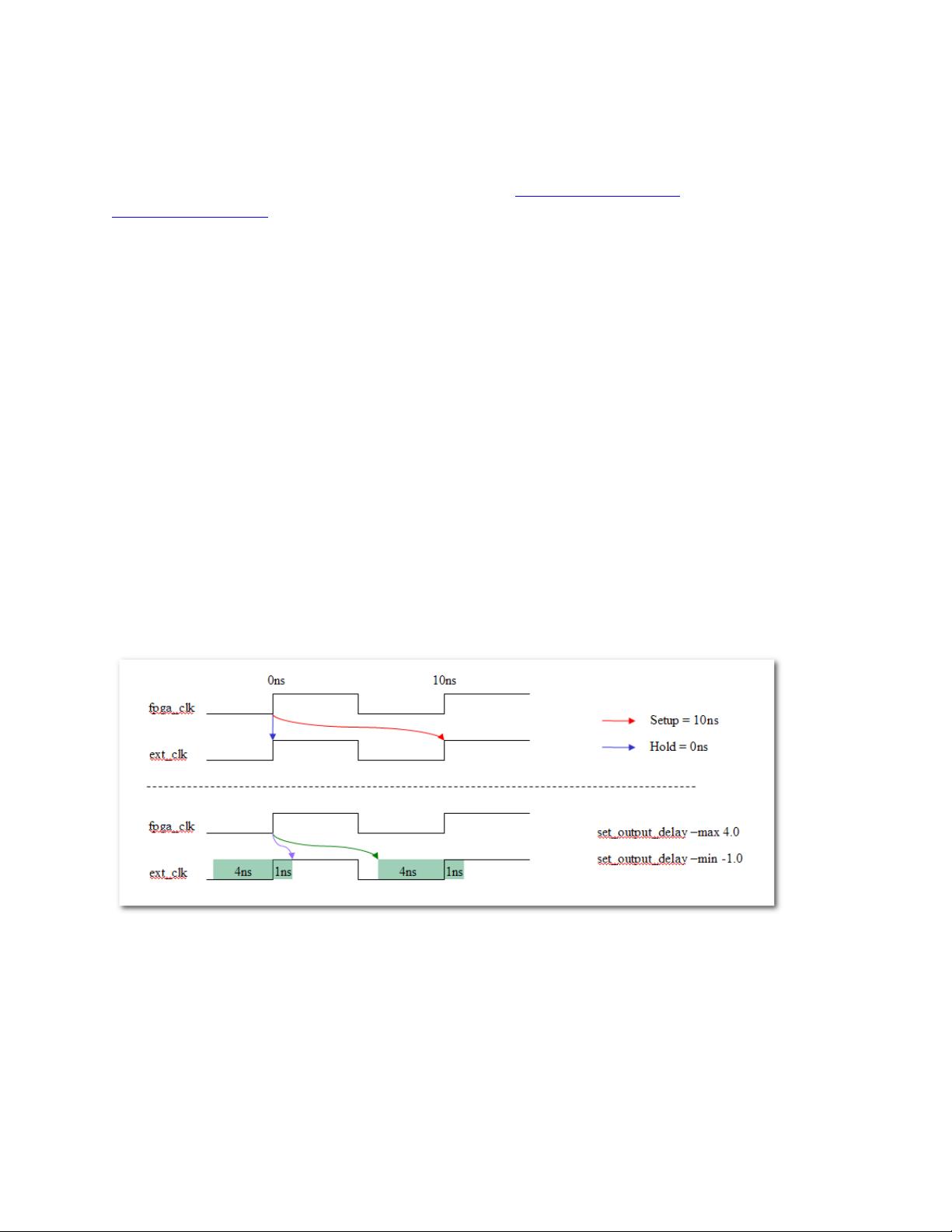

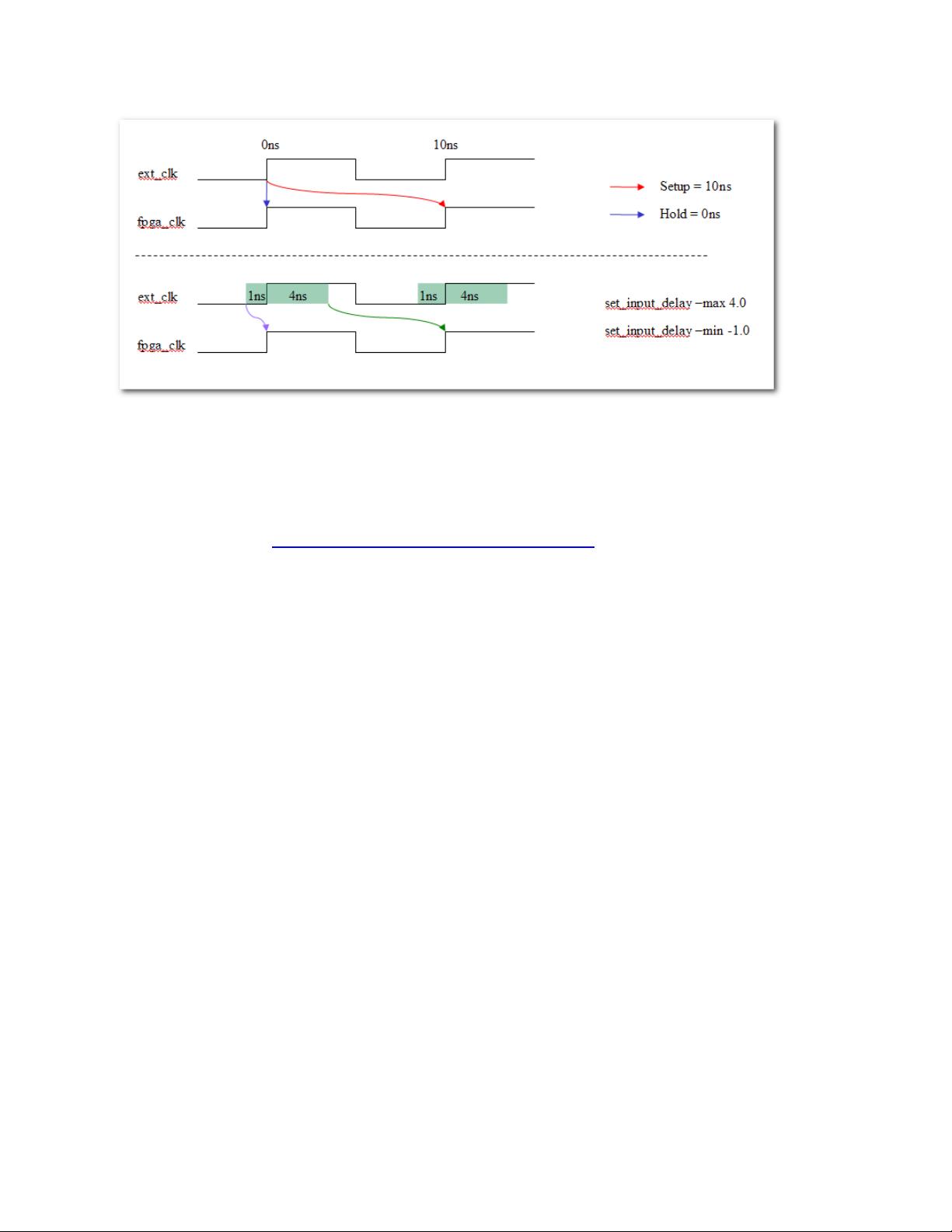

- **时序分析原理**:如何通过TimeQuest分析设计中的路径延迟,确保信号在预定时间内正确传输,避免潜在的设计错误。

- **逻辑优化**:通过分析报告理解设计中的瓶颈,进行逻辑优化,如布线优化、级联或阵列化等。

- **时钟树分析**:检查时钟网络的延迟和扇出,确保时钟同步和稳定性。

- **功耗管理**:识别功率消耗高的区域,有助于实现低功耗设计。

- **仿真与实际硬件行为比较**:使用TimeQuest与门级仿真工具进行对比,验证设计的预期行为。

- **性能指标**:学习如何解读和优化关键性能指标,如最大频率、最小时钟周期等。

随着时间的推移,作者计划持续更新文档,填补遗漏的部分,使其成为FPGA设计者进行时序分析的权威参考。掌握TimeQuest分析对于任何进行Altera FPGA设计的人来说,都是提升设计质量和效率不可或缺的技能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

107 浏览量

2021-10-02 上传

129 浏览量

113 浏览量

2021-03-06 上传

2021-05-28 上传

altera_jack

- 粉丝: 0

- 资源: 1

最新资源

- hello-webauthn

- 钢琴3D模型素材

- spec-prod:GitHub Action构建ReSpecBikeshed规范,验证输出并发布到GitHub页面或W3C

- xlsrange:从行号和列号生成一个excel范围-matlab开发

- C#使用Redis内存数据库

- XX公司组织架构说明书DOC

- 雨棚3d模型设计

- multiple-theme-switcher-website

- 电力及公用事业行业月报月全社会用电量同比增长长江三峡来水情况改善明显-19页.pdf.zip

- Conway's Game of Life:基于 Conway 的四个规则生成细胞群并研究其行为的接口。-matlab开发

- gulp:自己gulp练习

- 带反射面板的远距离光束中断传感器-项目开发

- 现代企业员工培训与开发的实施模型DOC

- lab-bucket-list

- 苹果专卖店三维模型设计

- jshelp:Javascript 帮助