FPGA高级时序综合教程:设置约束关键指南

“FPGA高级时序综合教程,关注于如何在FPGA设计中设置有效的时序约束,以优化性能和满足设计要求。”

在FPGA设计中,时序综合是至关重要的一步,它涉及到如何将逻辑设计转化为能够在目标硬件上正确并高效运行的物理实现。这个高级时序综合教程旨在帮助开发者更好地理解和应用时序约束,确保设计的时序性能达到预期。

首先,我们要理解什么是约束(Constraints)。约束是设计师对FPGA实现过程中的特定要求,比如时钟速度、信号延迟、I/O接口速度等。它们指导合成工具如何分配逻辑资源,以满足设计的时序和功能需求。常见的约束类型包括时钟约束、路径约束、I/O约束等。

时钟约束是最基础也是最重要的,它定义了系统时钟的周期、相位和偏移。例如,PERIOD关键字用于设定时钟信号的周期,HIGH和LOW则用于指定时钟信号的高电平和低电平持续时间。时间单位可以是ns或ps,表示纳秒和皮秒。

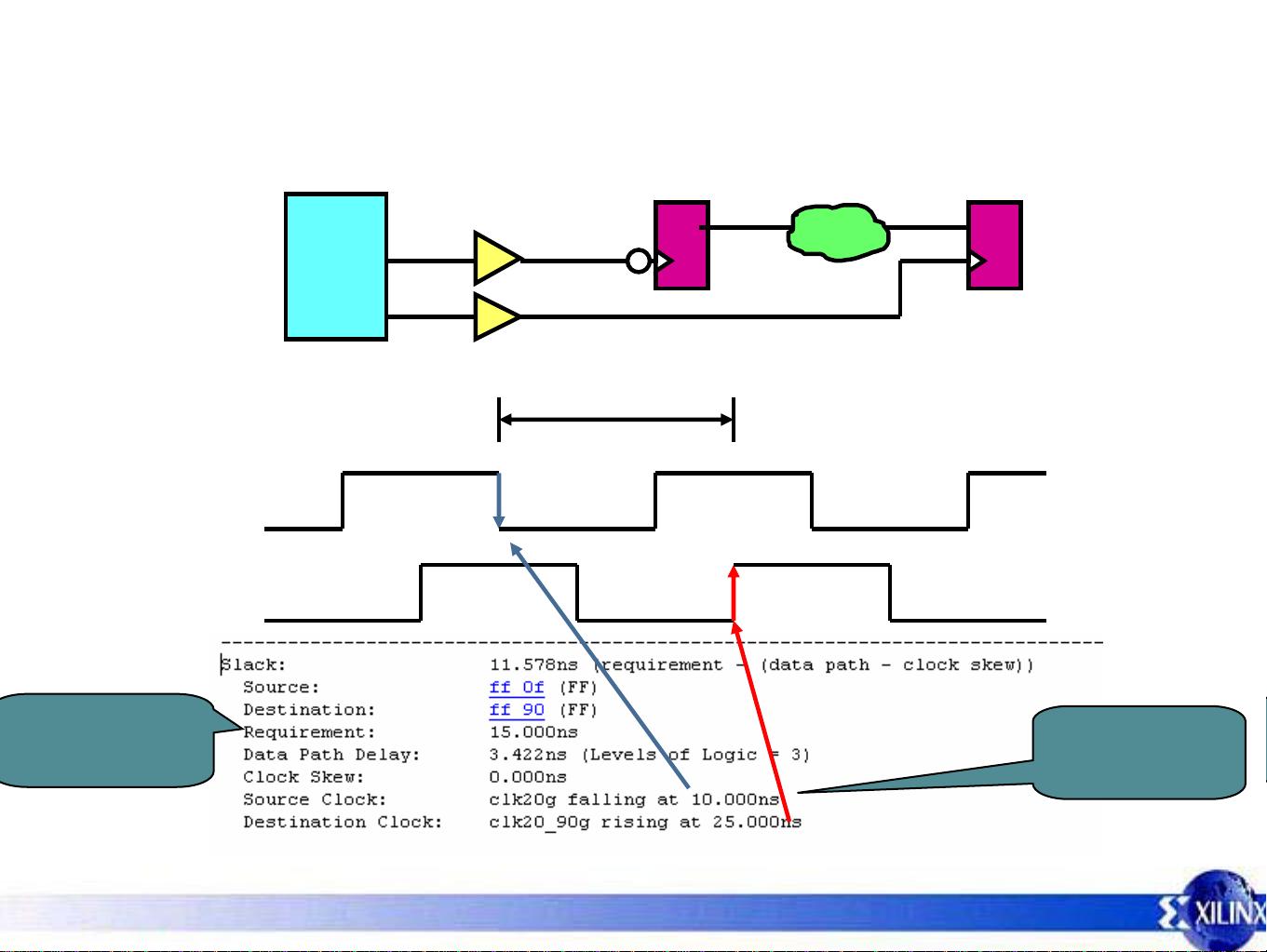

接下来是基本的时序约束,这包括路径约束,它定义了设计中关键路径的延迟限制。通过设置这些约束,设计师可以确保关键路径的延迟不超过允许的最大值,从而保证整个系统的时钟速度。

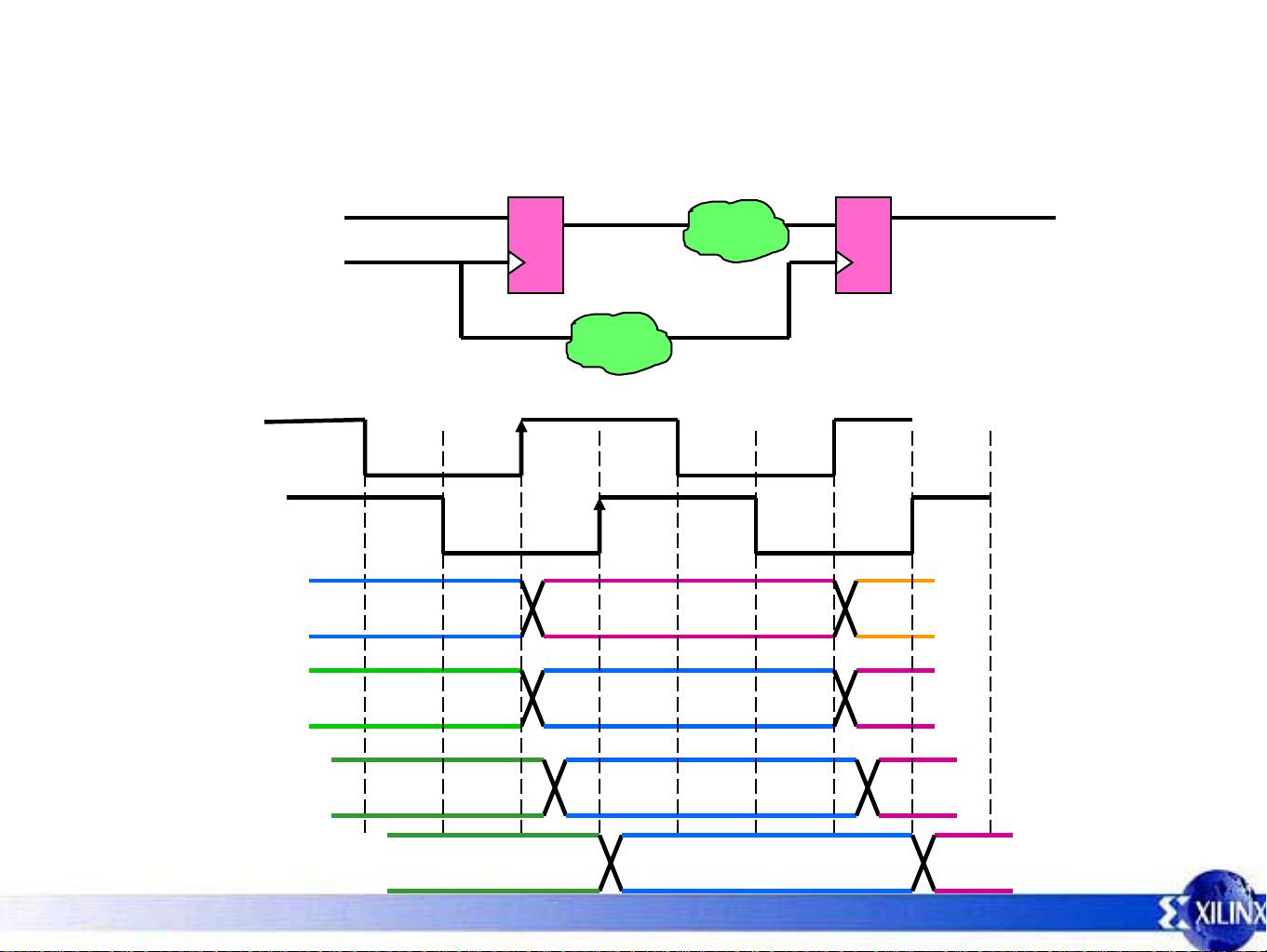

建立分组是另一种有效的约束技术,它允许将多个逻辑单元分组到一起,以便它们共享相同的时钟域或者有特定的时序关系。这种方法有助于优化布线资源,提高设计性能。

教程中还提到了其他类型的约束,如电源电压约束、I/O标准约束等。电源电压约束确保了芯片不同部分的电源配置符合设计要求,而I/O标准约束则定义了输入输出端口的工作模式,如LVCMOS、LVDS等。

约束优先级是一个重要的概念,它决定了当存在多个相互冲突的约束时,哪个约束会被优先考虑。理解并正确设置约束优先级是确保设计成功的关键。

整个流程从设计的逻辑域开始,经过翻译、时序分析(TRCE)、FPGA编辑、网表生成(XNF/EDIF netlist)、用户约束文件(UCF)、综合工具(NGDBUILD)、映射(MAP)、部分布局与布线(PAR),最终形成网络配置文件(NCF)和物理约束文件(PCF)。每个步骤都需要考虑相应的时序约束,以确保设计的完整性和性能。

这个FPGA高级时序综合教程深入探讨了如何有效地设置和管理约束,以优化FPGA设计的时序性能,是FPGA开发者的宝贵参考资料。通过学习和实践这些知识,开发者能够更准确地控制设计的时序行为,从而提高系统的整体效率和可靠性。

132 浏览量

137 浏览量

345 浏览量

点击了解资源详情

点击了解资源详情

236 浏览量

yoruichi924

- 粉丝: 0

- 资源: 5

最新资源

- 吉菲探索者

- 保险行业培训资料:地县级地区中端福寿连连销售逻辑

- frontend-react

- IEC101-103-104规约分析程序.rar

- 保险行业培训资料:从需求的角度看产品

- rms-list-gen

- DIU:乌苏里奥大学接口处

- tinyMCE:向 WordPress TinyMCE 添加自定义按钮

- 创维电视酷开系统14U系列8S26刷机应用工具包

- hex-to-rgb:将彩色十六进制值转换为rgb

- my-gridsome-app

- nexus-3.20.1-01-win64.rar

- nwis:对 nw.js GUI API 的 IntelliSense 支持

- materiaFramework:项目构建器,基于html POST请求

- IM Café-开源

- conquer_the_world:【打天下篇】工作知识纪要