VHDL设计基础教程:常数、变量、信号解析

需积分: 3 75 浏览量

更新于2024-08-01

收藏 609KB PPT 举报

"该资源是关于VHDL设计初步的学习资料,主要讲解了VHDL中的数据对象,包括常数、变量、信号及其在进程中的使用。内容涵盖常数定义、变量声明、信号声明以及它们在VHDL设计中的作用和区别。"

VHDL是一种硬件描述语言,用于数字系统的建模和仿真。本资料主要关注VHDL设计的基础,重点讲解了四个关键概念:常数、变量、信号和它们在进程中的应用。

1. **常数(CONSTANT)**:常数在VHDL中用于表示不可更改的值。例如,CONSTANT FBT: STD_LOGIC_VECTOR := "010110"; 定义了一个名为FBT的常数,其数据类型为STD_LOGIC_VECTOR,并赋值为"010110"。另一个例子CONSTANT DATAIN: INTEGER := 15; 声明了一个名为DATAIN的整数常数,值为15。

2. **变量(VARIABLE)**:变量用于在VHDL程序中存储可变的值。例如,VARIABLE a: INTEGER RANGE 0 TO 15; 定义了一个名为a的变量,其数据类型为整数,取值范围从0到15。变量的赋值可以通过赋值语句如VARIABLE x, y: INTEGER RANGE 15 DOWNTO 0; x := 11; y := 2 + x; 实现。

3. **信号(SIGNAL)**:信号在VHDL中模拟硬件连接,用于不同组件之间的通信。比如,SIGNAL a, b, c, y, z: INTEGER; 声明了五个整数类型的信号。在进程中,信号的赋值通过<=操作符进行,并且可以包含AFTER时间量来指定延迟,如y <= a + b AFTER 10 ns;。示例还展示了PROCESS如何处理信号,如y <= a + b; 和 z <= c - a;。

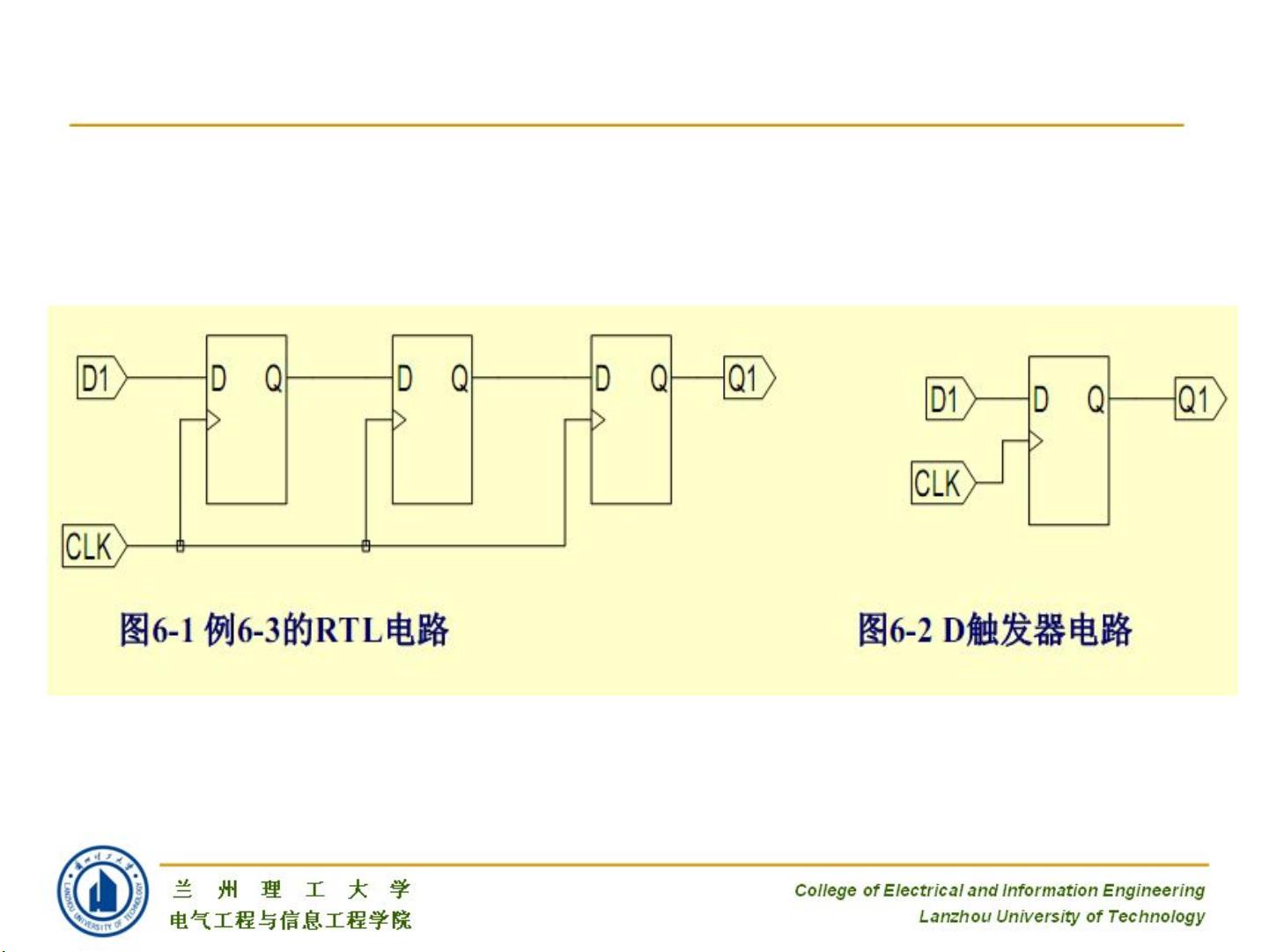

4. **进程(PROCESS)**:进程是VHDL中用来描述时序逻辑的关键构造。在进程中,变量用于临时存储计算结果,而信号赋值则发生在进程的最后。例如,PROCESS (CLK) 定义了一个与CLK信号相关的进程,其中DECLARE了一個变量QQ,并在CLK上升沿时将D1的值赋给QQ。进程结束后,Q1被赋值为QQ的当前值。

理解这些基本数据对象和进程的概念对于VHDL设计至关重要,因为它们构成了硬件行为描述的基础。常数用于固定不变的参数,变量用于存储临时计算结果,而信号则模拟实际硬件中的信号传输。掌握这些知识后,开发者能够更好地设计和模拟数字系统。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-06-11 上传

2021-10-07 上传

2021-10-07 上传

2021-10-07 上传