Verilog实现4x4位乘法器设计详解及Quartus仿真

需积分: 33 51 浏览量

更新于2024-09-03

收藏 76KB DOC 举报

本资源主要介绍了如何使用Verilog语言进行数字电路设计,具体是针对一个4bit*4bit的乘法器实现。设计过程包括以下几个关键部分:

1. Verilog语言基础:文章首先阐述了Verilog在数字电路设计中的应用,这是一种硬件描述语言,用于描述电子系统的逻辑功能。设计目标明确,即实现一个4位乘法器,它将涉及复杂的逻辑运算。

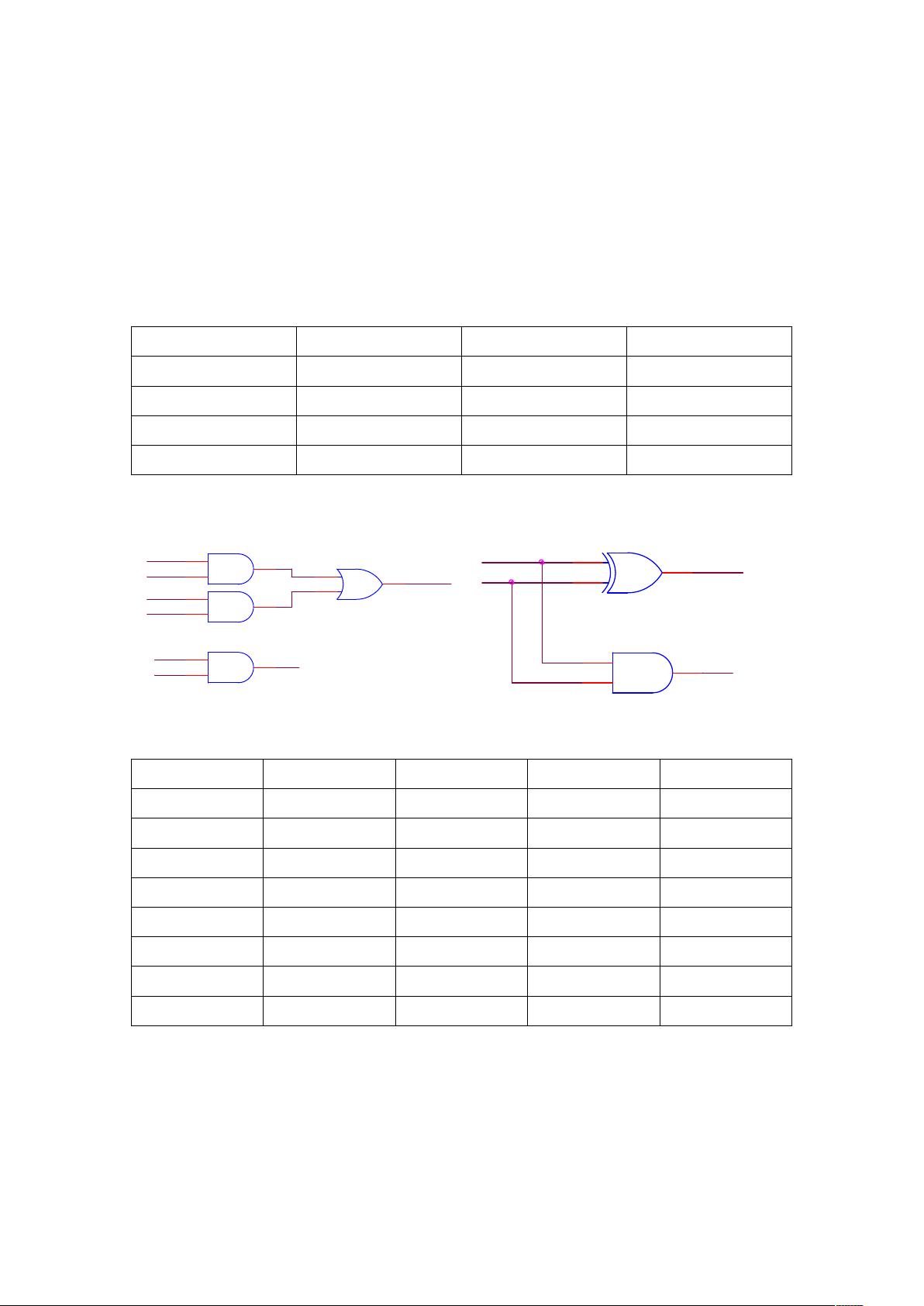

2. 半加器设计:半加器是乘法器的基础模块,它接受两个输入(X和Y),并产生一个进位输出C和一个和输出S。其基本工作原理是根据真值表进行逻辑计算,输出结果遵循逻辑代数规则。半加器的设计有助于理解更复杂的逻辑结构。

3. 全加器设计:全加器是在半加器基础上增加了一个额外的输入Z,用于处理进位。全加器通过逻辑组合简化为三个输入(X、Y、Z)的逻辑表达式,输出进位C和和S。电路图显示了全加器的实现方式,利用半加器和门电路构建。

4. 多位二进制加法实现:

- 行波进位加法器:这种设计方法结构简单,但速度较慢,进位传播时间随着位数增加而延长。最长延迟由最低有效位到最高有效位的传播决定。

- 超前进位加法器:也称为预进位加法器,通过预先计算进位来提高速度。它利用Pi(进位产生)和Gi(进位传输)的概念,使得进位可以在下一级加法器之前确定,从而缩短总延迟。

5. 仿真验证:设计完成后,使用Quartus工具编写程序,并通过modelsim等工具进行仿真验证,确保乘法器的逻辑功能正确无误。

总结来说,本资源详细讲解了从基础的半加器和全加器到多位二进制乘法器设计的全过程,涉及到Verilog编程、逻辑设计、以及实际硬件实现的仿真验证,对于学习数字电路设计的学生或工程师具有很高的参考价值。

2013-10-20 上传

2022-07-08 上传

2013-05-04 上传

2012-12-05 上传

2022-07-07 上传

2022-07-06 上传

2021-10-06 上传

succguan

- 粉丝: 3

- 资源: 6

最新资源

- MCP C#试用试题

- nutch初学入门 非常好的入门教程

- c#面试题 网络转载 不错 经典

- C#设计模式大全 好书

- Struts+Spring+Hibernate整合教程.pdf

- BP神经网络原理及仿真实例

- 使用简介POWERPLAY

- Oracle 9i10g编程艺术

- scm手把手开发文档

- Cognos Impromptu

- LoadRunner安装手册.pdf

- cognos 部署 文档

- 用C语言进行单片机程序设计与应用

- Direct3D.ShaderX.-.Vertex.and.Pixel.Shader.Tips.and.Tricks.pdf

- 《uVision2入门教程》.pdf

- spring1.2申明式事务.txt