FPGA中的MicroBlaze软核处理器与FSL总线应用解析

需积分: 9 66 浏览量

更新于2024-09-27

收藏 394KB DOC 举报

"本文主要探讨了FSL总线IP核在MicroBlaze软处理器系统中的应用,MicroBlaze是Xilinx公司为FPGA器件设计的32位RISC架构软核处理器,具备高速处理能力。文章阐述了FSL总线的特点、结构、工作原理和配置方法,强调了它在连接用户自定义IP核与处理器内部寄存器间的高速直连作用。此外,通过一个FPGA片上系统设计实例展示了如何利用FSL总线加速硬件执行。"

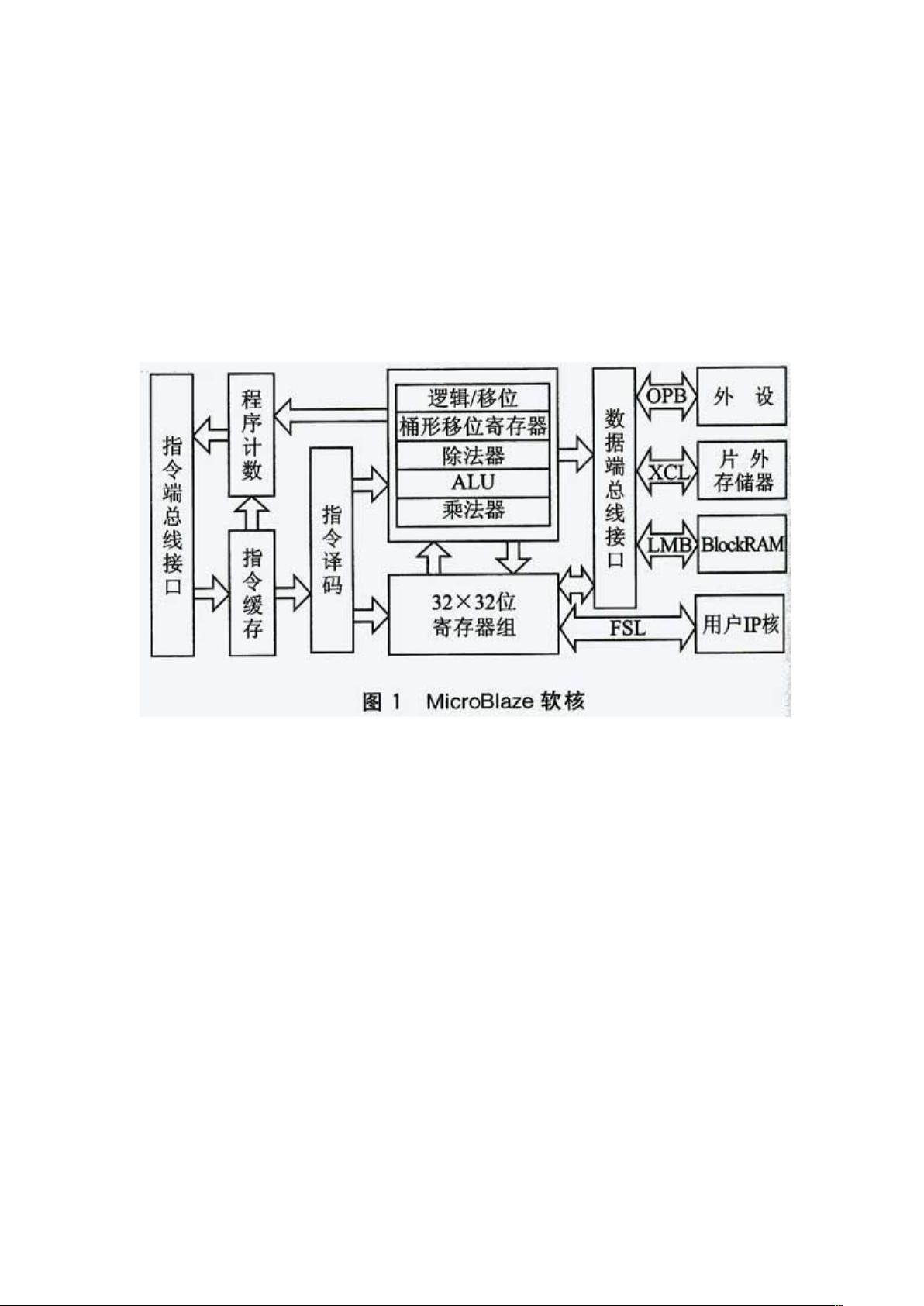

MicroBlaze软核处理器是一种高度灵活的嵌入式处理器,适用于Xilinx公司的FPGA器件。它采用精简指令集计算(RISC)架构和哈佛结构,拥有32个32位通用寄存器,可在150MHz时钟频率下实现125 DMIPS的处理性能。设计者可以通过Xilinx的EDK工具套件轻松定制和配置MicroBlaze处理器,这使得用户可以将自定义IP核集成进系统,实现硬件加速。

MicroBlaze的一大特色是它的FSL(Fast Simplex Link)总线。FSL总线是一种FIFO单向链路,用于高效地连接用户自定义的IP核与MicroBlaze的通用寄存器,从而实现高速数据传输。这种总线接口设计简化了系统设计,提高了系统的数据处理速率。

文章中详细分析了FSL总线的结构,包括其单向通信特性,以及如何配置以适应不同应用场景。FSL总线的工作原理涉及到数据包的打包、传输和解包,确保数据在FPGA内部的高效流动。配置FSL总线涉及设置合适的时序参数,以保证与其他系统组件的同步。

为了进一步说明FSL总线的应用,文中给出了一个具体的例子——矢量汉字还原应用。在这个案例中,FSL总线被用来整合用户设计的IP核,用于处理汉字矢量数据,从而显著提高了处理速度。这种方法展示了在FPGA片上系统设计中,如何利用FSL总线来优化硬件资源,提升系统性能。

此外,MicroBlaze支持多种接口标准,包括AXI、APB等,这些接口允许MicroBlaze与各种外设和存储器进行通信。这增强了MicroBlaze在复杂系统集成中的适应性,使得开发者可以根据需求选择最适合的接口进行设计。

FSL总线IP核是MicroBlaze系统中的关键组成部分,它提供了高效的IP核与处理器之间的连接,有助于实现硬件加速,提高整体系统的处理效率。对于基于FPGA的嵌入式系统设计者来说,理解并熟练运用FSL总线能够极大地提升其设计能力和系统性能。

2022-08-04 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-07-23 上传

2011-02-09 上传

2011-03-07 上传

2011-07-01 上传

点击了解资源详情