FPGA实现BP神经网络图像压缩的并行乘累加单元设计

14 浏览量

更新于2024-08-29

收藏 369KB PDF 举报

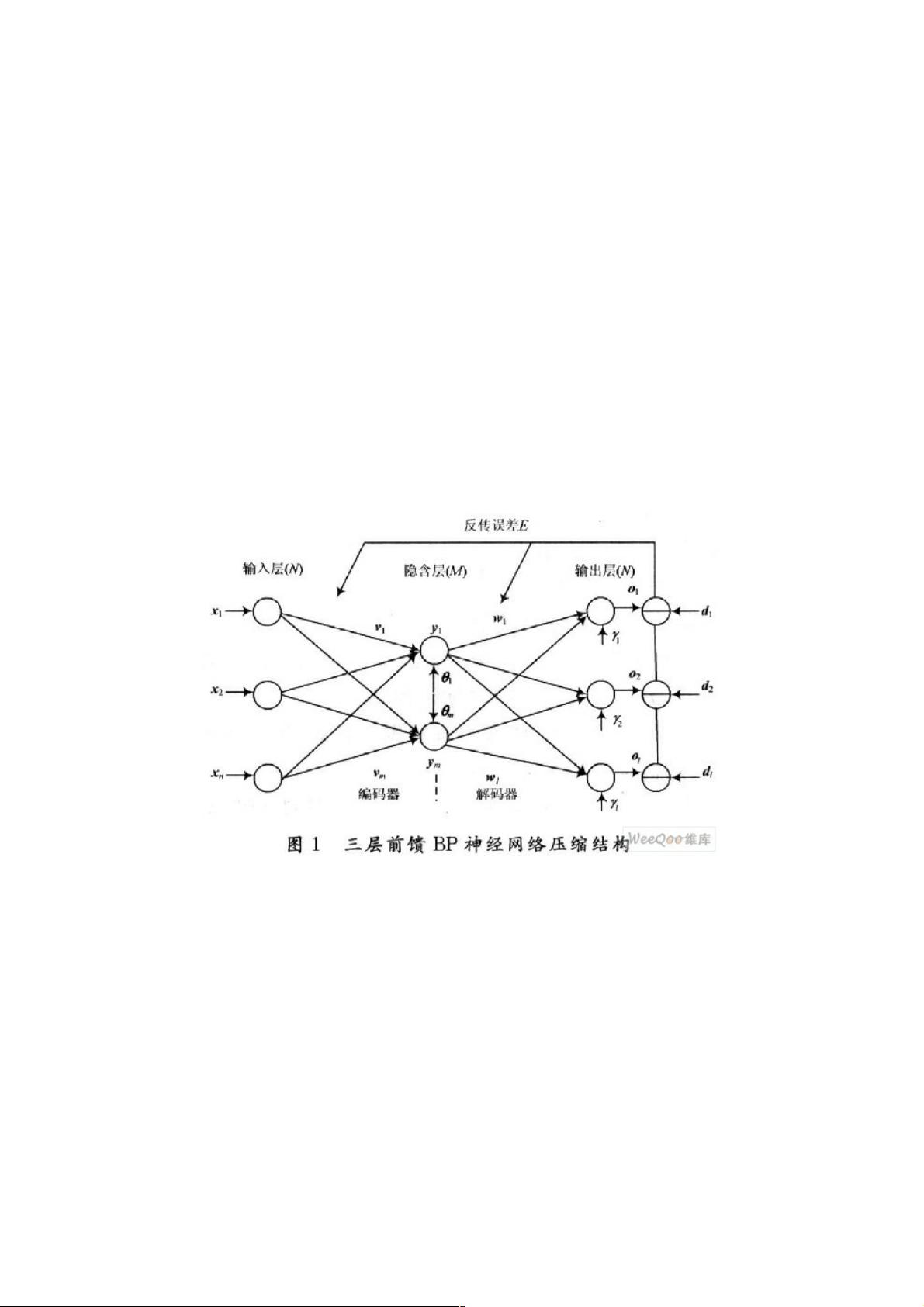

本文主要探讨了BP神经网络在图像压缩领域的应用,特别是在FPGA(现场可编程门阵列)中的设计实现。BP神经网络,因其采用反向传播算法(Back Propagation,BP),在处理图像数据时展现出强大的信息处理能力和自适应学习特性。人脑对图像信息的高效处理能力启发了研究人员将神经网络技术应用于图像压缩,以模仿大脑的并行处理和自组织特性。

在传统图像压缩方法如JPEG中,处理过程通常依赖于固定规则和算法。相比之下,BP神经网络通过训练能够自动调整权重,以优化图像的压缩效率和重建质量。FPGA作为硬件平台,因其高度并行性和灵活性,非常适合承载这种高度并行且可定制的神经网络计算任务。相比于专用的数字信号处理器(DSP),FPGA可以动态地分配硬件资源,提高数据处理速度,减少功耗。

文章详细介绍了FPGA在BP神经网络图像压缩算法中的关键组件,如乘累加单元的设计。乘累加单元是神经网络计算的基础,负责处理神经元之间的连接权重和输入信号的加权求和。在FPGA上实现这些单元,需要考虑硬件资源的优化配置,例如使用查找表(LUT)和触发器来高效实现乘法和累加操作,同时还要考虑到面积、延迟和能耗的平衡。

设计过程中,需要对神经网络的架构进行优化,比如选择合适的层数、节点数量以及优化网络拓扑,以适应FPGA的逻辑资源。此外,训练过程可能也需要在FPGA上进行部分或全部,以实现实时或在线学习,进一步提高压缩性能。

总结来说,本文的核心内容是BP神经网络在图像压缩中的应用策略,特别是如何利用FPGA的优势来实现高效的乘累加单元,以及如何优化FPGA设计以适应神经网络的复杂性和实时性需求。这是一项重要的研究,对于提高图像压缩系统的性能和效率具有重要意义,也为未来在其他领域如机器视觉、自动驾驶等的应用提供了借鉴。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-11-09 上传

2014-02-06 上传

2021-07-13 上传

2021-09-26 上传

2021-12-10 上传

2021-09-25 上传

weixin_38558186

- 粉丝: 4

- 资源: 878

最新资源

- WordPress作为新闻管理面板的实现指南

- NPC_Generator:使用Ruby打造的游戏角色生成器

- MATLAB实现变邻域搜索算法源码解析

- 探索C++并行编程:使用INTEL TBB的项目实践

- 玫枫跟打器:网页版五笔打字工具,提升macOS打字效率

- 萨尔塔·阿萨尔·希塔斯:SATINDER项目解析

- 掌握变邻域搜索算法:MATLAB代码实践

- saaraansh: 简化法律文档,打破语言障碍的智能应用

- 探索牛角交友盲盒系统:PHP开源交友平台的新选择

- 探索Nullfactory-SSRSExtensions: 强化SQL Server报告服务

- Lotide:一套JavaScript实用工具库的深度解析

- 利用Aurelia 2脚手架搭建新项目的快速指南

- 变邻域搜索算法Matlab实现教程

- 实战指南:构建高效ES+Redis+MySQL架构解决方案

- GitHub Pages入门模板快速启动指南

- NeonClock遗产版:包名更迭与应用更新