华为大规模逻辑设计指南:VHDL与Verilog编程技巧

需积分: 32 117 浏览量

更新于2024-07-24

收藏 3.45MB PDF 举报

大规模逻辑设计指导书是一份详细的文档,主要针对华为在IT行业的逻辑设计实践提供指导。该文档共140页,主要涵盖以下几个核心知识点:

1. **命名习惯与规则**:

- 介绍设计中信号和变量命名的重要性,强调应选择具有明确含义的名字,如包含信号来源、功能或状态等信息,如"inputSourceSignal",以便于理解和维护。

2. **编程语言元素**:

- **Verilog**:包括Verilog语言的基本结构,如`case`语句、`IF`语句、表达式、模块(`modules`)等,并提供了范例来展示如何正确编写。

- **VHDL**:介绍了VHDL的保留字,以及函数、程序包(`package`)和参数化元件实例的写作规范。

- **运算符(operators)**:涵盖了不同类型的运算符及其用法。

3. **代码编写规范**:

- **代码模块划分**:提倡将代码组织成模块化的结构,以提高可读性和可维护性。

- **代码注释**(`comments`):强调了注释在文档化的价值,以及如何有效地使用`FSM`(有限状态机)来表示状态转换。

- **资源管理和风格指南**:比如`TAB`键间距的使用,以及如何编写清晰、一致的代码风格。

4. **逻辑设计中的注意事项**:

- 避免使用`Latch`,因为它们可能导致潜在的问题。

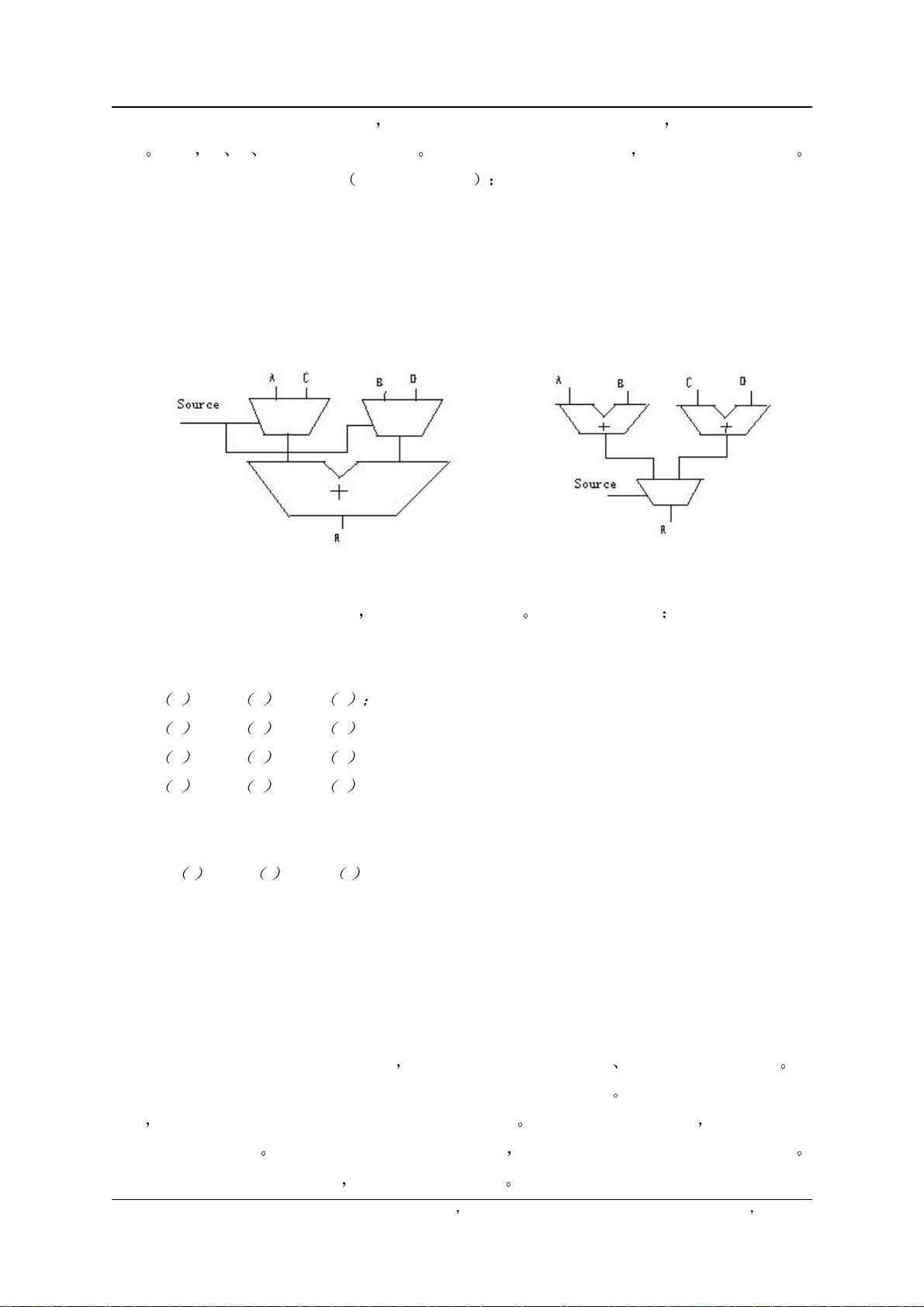

- 提供了关于组合逻辑描述的多种方式和执行时间考虑的建议。

- 解释了`combinatorial logic`(组合逻辑)与`sequential logic`(顺序逻辑)的区别,以及`macros`(宏)的使用。

5. **错误和问题**:

- 列出了代码编写过程中可能遇到的一些常见问题,如参数化元件实例的正确使用、资源共享问题,以及如何避免潜在的设计陷阱。

6. **版本管理和保密性**:

- 文档具有一定的机密级别,明确了文档的版本、日期、批准人和审核人的信息,以及版权和保密声明。

通过这份指导书,华为员工可以系统地学习和遵循逻辑设计的最佳实践,确保设计的质量和一致性。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2011-02-18 上传

2009-10-13 上传

2021-09-20 上传

2021-12-18 上传

2009-07-14 上传

逆鳞92

- 粉丝: 2

- 资源: 5

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍

已收录资源合集

已收录资源合集