FPGA实现的数字脉冲压缩系统:功能与硬件设计

80 浏览量

更新于2024-08-30

3

收藏 315KB PDF 举报

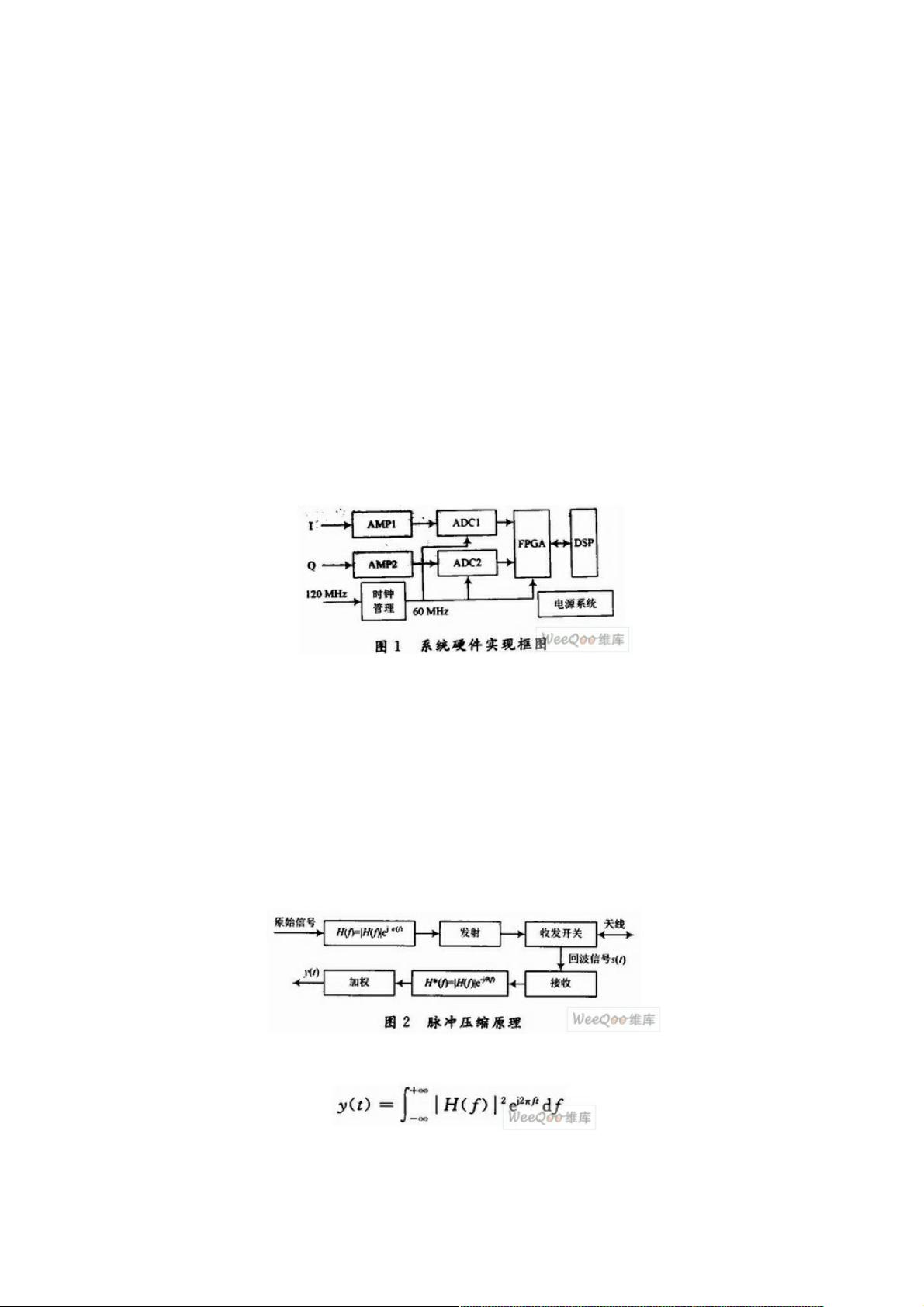

本文主要探讨了基于FPGA的数字脉冲压缩系统在现代雷达技术中的应用与实现。脉冲压缩是雷达系统的关键组成部分,它通过在发射端使用宽脉冲提升功率,确保远距离探测,而在接收端通过脉冲压缩算法减小脉冲宽度,从而增强距离分辨率。线性调频(LFM)信号因其对多普勒频移的低敏感性而被广泛选择,它通过载波线性调制来扩大信号带宽,实现高压缩比。

文章的核心在于利用快速傅里叶变换(FFT)的IP核在FPGA上的可复用性和灵活性,设计了一种频域的数字脉冲压缩处理器。这种处理器可以处理正交输入的可变点LFM信号,具备了设计的灵活性、易于调试以及良好的可扩展性。硬件实现上,系统包括数据采集部分,如运算放大器AD8138用于信号转换和模数转换器ADS5500进行高速采样,确保60MHz的采样速率。数字脉冲压缩模块则在Xilinx XQ2V1000 FPGA中实现,压缩后的数据存储在双口RAM中,并通过中断机制与DSP通信,进行后续的信号处理。

整个系统的设计目标是在一个脉冲重复周期内完成数据采集和压缩,同时保证数据传输的实时性和准确性。这种基于FPGA的解决方案不仅提高了雷达系统的性能,还简化了硬件设计过程,便于维护和升级。通过对FPGA资源的有效利用,本文的方法对于提高雷达系统的效能和适应不断变化的需求有着重要意义。

2021-07-13 上传

2021-07-13 上传

2020-10-18 上传

2020-11-05 上传

2021-07-13 上传

2021-01-31 上传

2020-10-18 上传

2021-07-13 上传

weixin_38703895

- 粉丝: 4

- 资源: 910