Cortex-M3异常处理机制深度解析

51 浏览量

更新于2024-08-28

1

收藏 205KB PDF 举报

"Cortex-M3的异常处理机制研究"

Cortex-M3是ARM公司设计的一款基于ARMv7-M架构的微控制器内核,它在异常处理机制上相比早期的ARM7内核有显著的提升。在Cortex-M3中,异常处理机制被优化得更加高效,能够以12个时钟周期的响应时间处理异常,这得益于其内置的Nested Vectored Interrupt Controller (NVIC)。

NVIC是Cortex-M3的一个关键组成部分,它可以配置处理多达240个物理中断,并具有256个优先级和8级抢占优先权。这种设计使得处理器能够快速而有序地响应各种中断请求,从而提高了系统的实时性能。NVIC的嵌套向量特性意味着在中断发生时,它可以按照优先级顺序确定下一个要执行的服务程序。

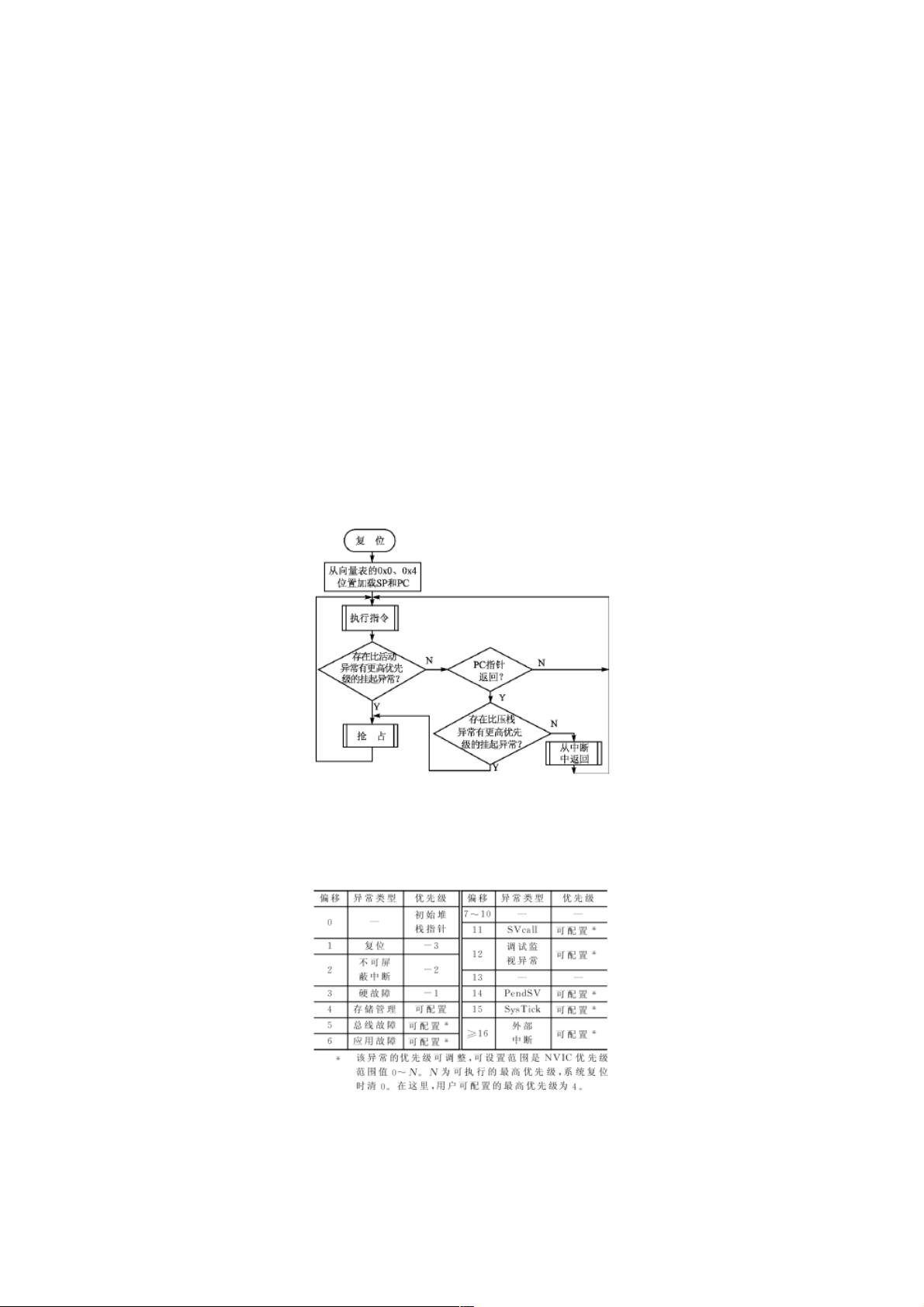

Cortex-M3异常处理机制的关键技术包括抢占、尾链和迟到。抢占允许高优先级的中断在低优先级中断处理过程中中断执行,确保更重要的事件得到及时响应。尾链技术则是在异常处理之间直接跳转,无需额外的指令来设置下一次跳转地址,这大大减少了处理时间。迟到技术则允许在异常处理开始后,如果新的更高优先级中断到达,系统可以立即切换到更高优先级的中断处理,而不需要等待当前处理的完成。

异常的分类在Cortex-M3中包括中断和系统异常,如软件中断、硬件中断、预取错误、数据访问错误等。每个异常都有一个相应的向量地址,用于指示异常处理程序的入口。当异常发生时,处理器会自动保存程序状态,包括PC、xPSR、LR和部分工作寄存器的值,然后跳转到异常处理程序。在ISR执行完毕后,处理器会恢复先前保存的状态,继续执行被中断的程序。

Cortex-M3与ARM7在异常处理上的主要区别在于,Cortex-M3利用硬件加速和优化的中断处理流程,显著减少了中断处理的开销。ARM7虽然也支持中断处理,但其响应时间和资源管理不如Cortex-M3高效。通过对迟到和尾链技术的量化分析,可以清楚地看到Cortex-M3在处理异常和中断时的性能优势,这对于实时性和响应速度要求高的应用至关重要。

Cortex-M3的异常处理机制是其强大功能的关键组成部分,它通过NVIC的灵活配置、高效的异常处理技术和优化的中断管理,为嵌入式系统提供了高效、可靠的运行环境。

1040 浏览量

1542 浏览量

767 浏览量

200 浏览量

点击了解资源详情

310 浏览量

点击了解资源详情

点击了解资源详情

310 浏览量

weixin_38709511

- 粉丝: 0

最新资源

- 易语言制作的内核变速器源码分享

- 基础HTML页面构建与 xdondeseenpiezaatodo6 主文件解析

- 实现ImageView手势缩放与图片下载的架构设计

- 线之绘风格滤镜——PS图片处理新境界

- CheatEngine5.6.1游戏内存修改工具详解

- Android开发:二维码生成器中间带Logo的实现方法

- SSH框架中文参考手册集合,助力快速开发

- 深入浅出JavaScript教程章节概览

- Ruby应用程序部署与运行指南

- 软解调软译码远程水声通信技术研究.zip

- 解决gmail无法使用问题的初音手上跳舞包下载

- 深入解析计算机网络基础与常见问题解决

- Android跨线程通信辅助库:AndroidChannel使用指南

- 毕业设计精华:运动估计与检测技术解析

- Hola Amigos!与Arsh Sahzad的统计数据分享

- 详解iMX6 Rex开发板PCB设计与AD文件结构