Cortex-M3异常处理机制优化:NVIC与中断响应研究

108 浏览量

更新于2024-08-29

收藏 212KB PDF 举报

"Cortex-M3内核的异常处理机制及其新技术研究"

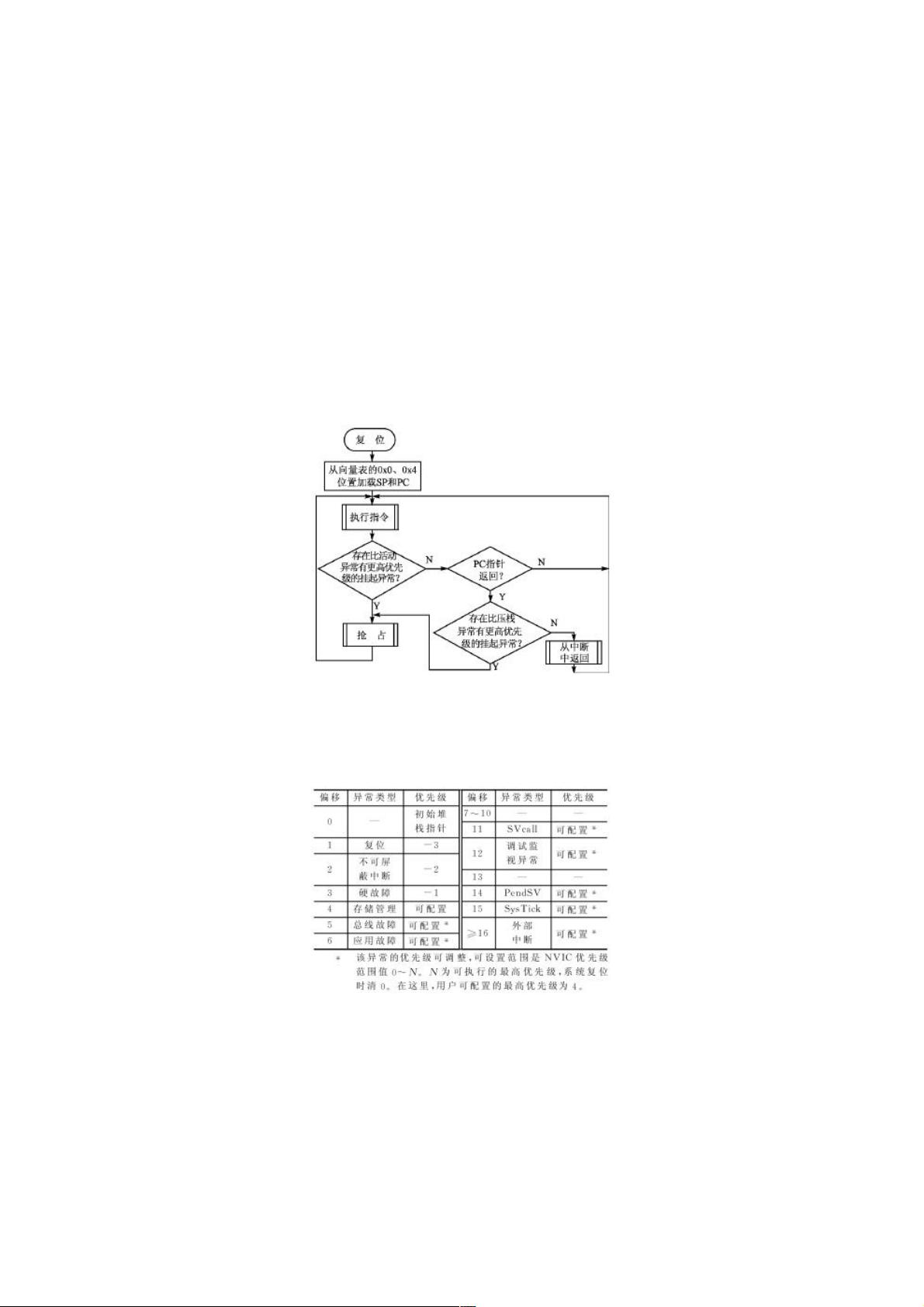

Cortex-M3是ARM公司的微控制器内核,基于ARMv7-M架构,它在很多方面与ARM7有显著区别,特别是在异常处理机制上。Cortex-M3内核异常处理的高效性体现在其仅需12个时钟周期即可响应异常,这得益于其内置的Nested Vectored Interrupt Controller (NVIC)。NVIC是一个集成的组件,能支持1到240个物理中断,每个中断拥有256个优先级级别和8级抢占优先权,确保处理器能够快速、灵活地处理各种中断事件。

NVIC的特性包括抢占(preemption)、尾链(tail-chaining)和迟到(late-arriving)技术。抢占允许更高优先级的中断打断正在执行的低优先级中断服务;尾链技术使得中断服务完成后可以直接跳转到下一个中断服务,无需额外的上下文切换开销;迟到技术则允许在中断响应后才计算中断向量,这样可以避免不必要的延迟。

在异常处理过程中,Cortex-M3通过硬件自动保存关键寄存器的状态,如编程计数器(PC)、编程状态寄存器(xPSR)、链接寄存器(LR)以及R0到R3和R12寄存器。同时,通过DBus保存处理器状态,Ibus则从可重定位的向量表中读取异常向量,找到对应的中断服务例程(ISR)地址。这种并行处理方式大大提高了处理速度。在ISR执行完毕后,硬件会自动恢复中断前的现场,使程序能够继续正常运行。

Cortex-M3的异常类型多样且具有明确的优先级。与ARM7不同,Cortex-M3的异常分类包括复位、系统挂起、硬fault、内存管理fault、总线fault、使用fault、预取数据fault、irq(中断)和fiq(快速中断),这些异常按照优先级排序,从高到低依次处理。这样的设计确保了系统对高优先级事件的优先响应,同时能够妥善处理各种类型的错误和中断请求。

Cortex-M3的异常处理机制通过NVIC、抢占、尾链和迟到等技术实现了高效的中断管理,增强了微控制器的实时性和可靠性,使其成为嵌入式系统设计中的理想选择。深入理解和掌握这些机制对于开发和优化Cortex-M3平台的应用至关重要。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-10-20 上传

2021-01-19 上传

2020-10-21 上传

2012-10-22 上传

2013-06-30 上传

2021-08-29 上传

weixin_38516491

- 粉丝: 6

- 资源: 950

最新资源

- vhdl实现三人表决器

- java struts教程

- 如何实现SQL SERVER 2008 的故障转移群集

- s60系列应用框架手册.pdf

- Hibernate开发指南

- JavaScript高级编程(CHS)

- DWR中文文档.pdf DWR中文文档.pdf

- 基于stc单片机出租车计价

- 深入了解MFC中的文挡/视结构.PDF

- 电子元件基础教程,本文简单介绍了一些电子元器件的概念和特性,对初学者有一定的帮助。

- arm architecture reference manual

- 《ZigBee概述》(中文版)

- Reversing C++

- 图的遍历#include <stdlib.h>

- Toad for Oracle

- ORACLE官方SQL教程中文版