没有合适的资源?快使用搜索试试~ 我知道了~

首页VHDL电路设计与模拟实战指南

"Circuit Design and Simulation with VHDL 2nd" 是一本关于使用VHDL进行电路设计和模拟的教材,由Volnei A. Pedroni撰写。这本书全面介绍了VHDL语言及其在实际、行业标准电路设计和模拟中的应用。作者强调了设计示例和实验练习,不仅关注VHDL语言本身,还展示了如何从语言构造中推断出特定类型的电路,并实现了四种模拟类别。书中明确区分了用于综合的VHDL和用于模拟的VHDL。 书中包含完整的VHDL代码设计示例,每个设计都配以电路图、FPGA物理综合结果、模拟输出以及解释性评论。此外,还有关于数字电子基础概念和设计的回顾,并附有多个附录,提供了ISE、Quartus II、ModelSim等重要设计工具的教程,以及实现设计的可编程逻辑设备的描述、DE2开发板、标准VHDL包等内容的介绍。 第二版是第一本详细分析所有四种VHDL测试平台(非自动化、完全自动化、功能性和时序模拟)的电路模拟的教科书,且提供了完整实践例子。前九章进行了更新,新增了设计示例和数据类型、代码语句等主题的新细节。第十章全新,专门讨论模拟。第十一到十七章也是全新的,涵盖了串行数据通信电路、视频电路等高级设计的理论和实践内容。书中的插图增多,练习题也进行了更新,数量翻倍。 本书适合电子工程和计算机科学的学生及专业工程师学习,帮助他们掌握VHDL语言,进行电路设计和模拟,适用于课程教学或自我学习。对于想要深入理解VHDL在现代电子系统设计中应用的人来说,这是一本宝贵的资源。

资源详情

资源推荐

including the analysis of o‰cial standards, when applicable. This part of the book replaces

chapters 8, 9 , and 12 of the previous edition. The main di¤eren ces are summarized below.

Chapter 11 presents detailed design techniques for finite state machines (FSMs) using

VHDL. A new technique for complex, timed machines is introduced in this new edition.

Another new topic discusses the state-bypass problem in FSMs. The result is the most

comprehensive study of FSM design using VHDL so far.

Chapter 12 is another completely new addition to the book. It presents a series of

designs involving basic displays (LEDs, SSDs, and LCDs). Because these devices provid e

physical (visual) feedback to the students, lab exercises involving them are very motivating.

As in all other chapters, each design is preceded by theoretical information on the circuits

to be designed.

Chapter 13, also new, shows a study of memory implementations. This is important be-

cause basically any modern digital system requires some sort of memory.

Chapter 14 is the longest of the new chapters. It deals with a very modern topic, present

in almost all large des igns, which consists of serial data communications circuits. Several

modern interfaces are described (I

2

C, SPI, TMDS, PS2) and subsequently used in actual

applications, driving actual ICs.

Chapters 15–17 are also new. All three deal with video circuits, again providing interest-

ing, advanced circuits for lab experiments. Chapter 15 deals with the traditional VGA in-

terface, used to connect computers to analog video monitors. Chapter 16 describes the

DVI interface, fully digital and much more complex, used to connect desktop computers

to LCD monitors. Finally, chapter 17 deals with the FPD-Link interface, which is a mod-

ern video interface for industrial and hand-held applications.

With Respect to the Exercises

The exercise sections were modernized and greatly exp anded (there were 96 exercises in the

previous edition; there are now 231). A broader coverage is ach ieved, with numerous inter-

esting exercises for implementation and testi ng in FPGA boards during the lab sections.

With Respect to the Overall Presentation

The text was fully revised and expanded, with a smoother presentation and the inclusion of

many additional details, both theoretical and practical. The same occurred with the fig-

ures, with the inclusion of many new ones and the complete reconstruction of those

brought over from the first edition.

Audience

The book is mainly intended for the following:

1

electrical engineering undergraduate and graduate students,

1

computer engineering undergraduate and graduate students,

xviii Preface

1

computer science undergraduate and graduate students,

1

digital design professors and instructors,

1

VHDL professors and instructors,

1

digital design engineers and practitioners in the industry, and

1

digital design consultants and other practitioners at all levels.

Companion Books

The following two references are highly recommended:

1

IEEE 2008 for additional details on the VHDL language.

1

Pedroni 2008 for theoretical background on digital concepts and digital circuits.

Preface xix

I

CIRCUIT-LEVEL VHDL

1

Introduction

1.1 About VHDL

This chapt er concisely describes what VHDL is and what it is used for. Popular synthesis

and simulation tools are also listed, and a typical design flow is summariz ed.

VHDL is a hardware description language. The code describes the behavior or structure

of an electronic circuit, from which a compliant physical circuit can be inferred by a com-

piler. Its main applications include synthesis of digital circuits onto CPLD/FPGA (Com-

plex Program mable Logic Device/Field Programmable Gate Array) chips and layout/

mask generation for ASIC (Application-Specific Integrated Circuit) fabrication.

VHDL stands for VHSIC (Very High Speed Integrated Circuits) Hardware Description

Language, and resulted from an initiative funded by the U.S. Department of Defense in the

1980s. Its first version was VHDL 87, later upgraded by VHDL 93, then VHDL 2002, and

finally VHDL 2008. It was the first hardware description language standardized by the

IEEE, through the 1076 and 1164 standards. VHDL is technology/vendor independent,

so VHDL codes are portable and reusable.

VHDL allows circuit synthesis as well as circuit simulation (both are covered in the

book). The former is the translation of a source code into a hardware structure that imple-

ments the intended functionality, while the latter is a testing procedure to ensure that such

functionality is indeed achieved by the synthesized circuit. In all chapters we will concen-

trate on VHDL constructs that are synthesizable, except for chapter 10, which deals exclu-

sively with VHDL for simulation.

1.2 VHDL Versions

The first VHDL version was released in 1987, through the IEEE 1076-1987 Standard

VHDL Language Reference Manual. Several versions followed (all listed below).

1

IEEE 1076-1987 Standard VHDL Language Reference Manual (archived)

1

IEEE 1076-1993 Standard VHDL Language Reference Manual (archived)

1

IEEE 1076-2000 Standard VHDL Language Reference Manual (archived)

1

IEEE 1076-2002 Standard VHDL Language Reference Manual (archived)

1

IEEE 1076-2008 Standard VHDL Language Reference Manual (active: released in Feb-

ruary 2009).

Other related documents, mainly with synthesis packages, are listed below.

1

IEEE 1164-1993 Standard Multivalue Logic System for VHDL Model Interoperability

(active)

1

IEEE 1076.3-1997 Standard VHDL Synthesis Packages (active)

1

IEEE 1076.6 Standard for VHDL Register Transfer Level (RTL) Synthesis (active).

Because the 2000 document was rapidly replaced with the 2002 version, it is usually con-

sidered that four VHDL versions exist: VHDL 87, VHDL 93, VHDL 2002, and VHDL

2008.

The expansions introduced in VHDL 2008 will be explained in the corresponding

chapters. The package-related additions will also be mentioned in the corresponding data

packages of appendices H–N.

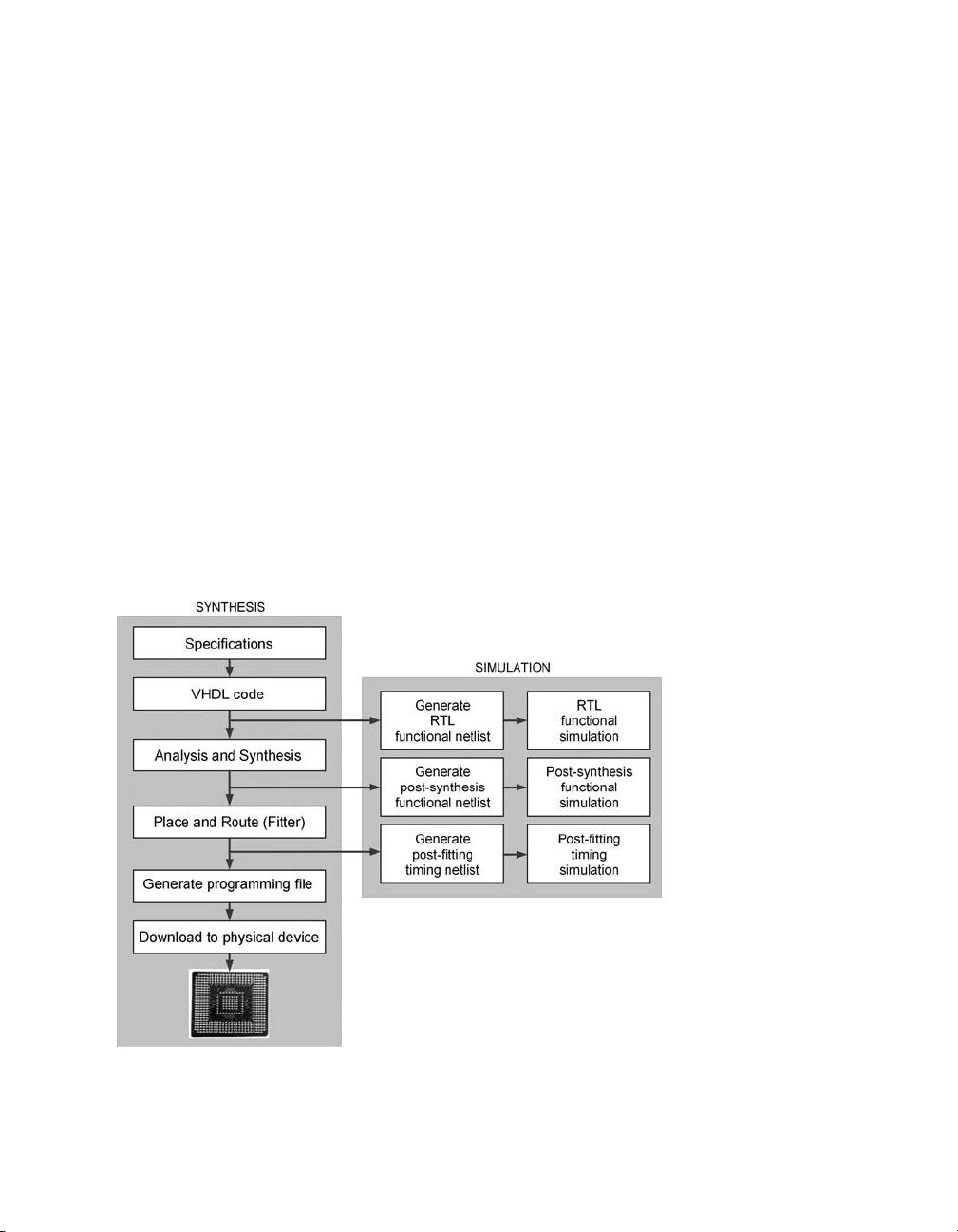

Figure 1.1

Simplified VHDL design flow.

4 Chapter 1

剩余607页未读,继续阅读

sinat_41581062

- 粉丝: 21

- 资源: 174

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 李兴华Java基础教程:从入门到精通

- U盘与硬盘启动安装教程:从菜鸟到专家

- C++面试宝典:动态内存管理与继承解析

- C++ STL源码深度解析:专家级剖析与关键技术

- C/C++调用DOS命令实战指南

- 神经网络补偿的多传感器航迹融合技术

- GIS中的大地坐标系与椭球体解析

- 海思Hi3515 H.264编解码处理器用户手册

- Oracle基础练习题与解答

- 谷歌地球3D建筑筛选新流程详解

- CFO与CIO携手:数据管理与企业增值的战略

- Eclipse IDE基础教程:从入门到精通

- Shell脚本专家宝典:全面学习与资源指南

- Tomcat安装指南:附带JDK配置步骤

- NA3003A电子水准仪数据格式解析与转换研究

- 自动化专业英语词汇精华:必备术语集锦

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功