FPGA实现的宽带数字接收机变带宽下变频器设计

149 浏览量

更新于2024-08-30

1

收藏 411KB PDF 举报

"基于FPGA的宽带数字接收机变带宽数字下变频器设计"

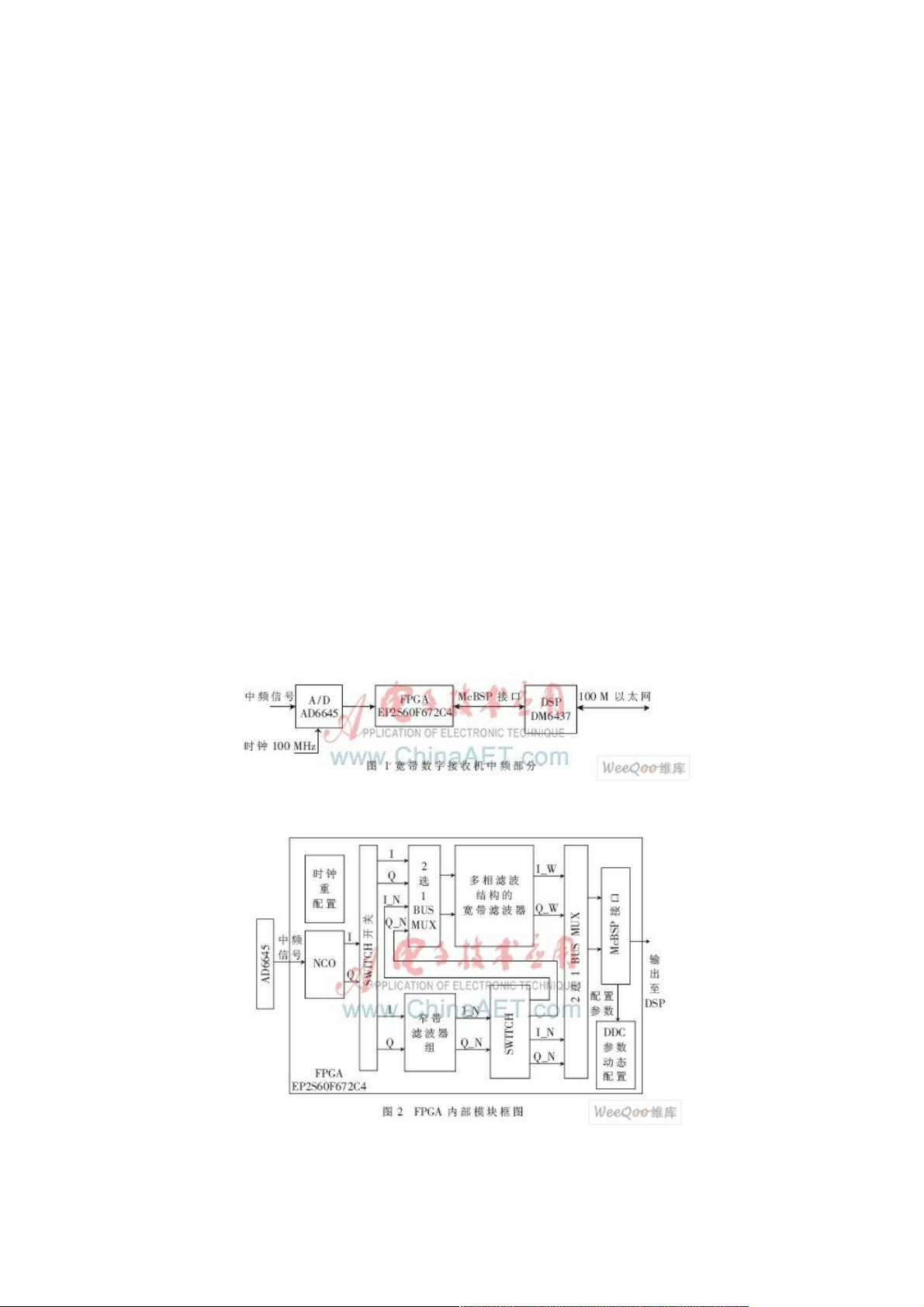

本文主要讨论了如何利用FPGA(Field-Programmable Gate Array)技术设计一个适用于宽带数字接收机的变带宽数字下变频器(VB-DDC),特别是基于Altera公司的Stratix II EP2S60F672C4芯片进行实现。VB-DDC是一种关键的信号处理组件,能够处理不同带宽的输入信号,因此在雷达、通信和电子侦察等众多领域中具有广泛的应用。

传统的数字下变频器(DDC)通常采用多级级联积分梳状滤波器(CIC)结构,尽管可以实现带宽调整,但其输入数据采样率有限,例如Intersil公司的HSP50214B,采样率仅为65 MHz,且最大处理带宽不超过1 MHz。这在处理宽带信号时显得不足。另一方面,基于多相滤波结构的DDC虽然能处理宽带信号,但带宽通常是固定的,且在处理窄带信号时,由于抽取因子增大,所需的乘法器数量增多,资源利用率下降,工作频率也会降低。

针对这些问题,本文提出的设计方案融合了传统DDC结构和多相滤波器的优点,以提高处理效率和灵活性。VB-DDC的设计目标是在保持高速处理能力的同时,能够在一个较大的范围内调整信号处理带宽。具体来说,当A/D转换器输出的中频信号采样率为100 MS/s时,VB-DDC能够将处理带宽设定在40 MHz到8 kHz之间,相应的输出基带信号数据率可在50 MS/s到112 kS/s之间灵活变换。

系统结构方面,VB-DDC通常包含预下变频、多相滤波器、抽取器和低通滤波器等核心部分。预下变频用于将中频信号转换到较低的频率范围,便于后续处理。多相滤波器则通过并行处理多个相位的信号来实现宽带信号的下变频。抽取器根据需要的带宽进行下采样,降低数据率。最后,低通滤波器用于消除高频噪声和图像信号,得到纯净的基带信号。

硬件调试结果证实了这种VB-DDC设计的有效性,它能够在不牺牲性能的前提下,满足不同应用场景对带宽的需求。这种灵活的带宽配置能力对于适应多任务、多标准的现代通信系统至关重要,能够显著提高系统的适应性和利用率。

基于FPGA的VB-DDC设计克服了传统和多相滤波结构的局限,提供了一种高效且灵活的解决方案,对于提升宽带数字接收机的性能和应用范围具有重要意义。未来的研究可能会进一步优化设计,比如减少资源消耗、提高处理速度或增强动态调整带宽的能力,以满足更复杂和苛刻的系统需求。

501 浏览量

196 浏览量

2021-07-13 上传

176 浏览量

1473 浏览量

135 浏览量

2021-07-13 上传

161 浏览量

145 浏览量

weixin_38576779

- 粉丝: 9

最新资源

- ITween插件实用教程:路径运动与应用案例

- React三纤维动态渐变背景应用程序开发指南

- 使用Office组件实现WinForm下Word文档合并功能

- RS232串口驱动:Z-TEK转接头兼容性验证

- 昆仑通态MCGS西门子CP443-1以太网驱动详解

- 同步流密码实验研究报告与实现分析

- Android高级应用开发教程与实践案例解析

- 深入解读ISO-26262汽车电子功能安全国标版

- Udemy Rails课程实践:开发财务跟踪器应用

- BIG-IP LTM配置详解及虚拟服务器管理手册

- BB FlashBack Pro 2.7.6软件深度体验分享

- Java版Google Map Api调用样例程序演示

- 探索设计工具与材料弹性特性:模量与泊松比

- JAGS-PHP:一款PHP实现的Gemini协议服务器

- 自定义线性布局WidgetDemo简易教程

- 奥迪A5双门轿跑SolidWorks模型下载