FPGA Stratix II 实现宽带数字接收机带宽可调VB-DDC设计

13 浏览量

更新于2024-08-30

收藏 356KB PDF 举报

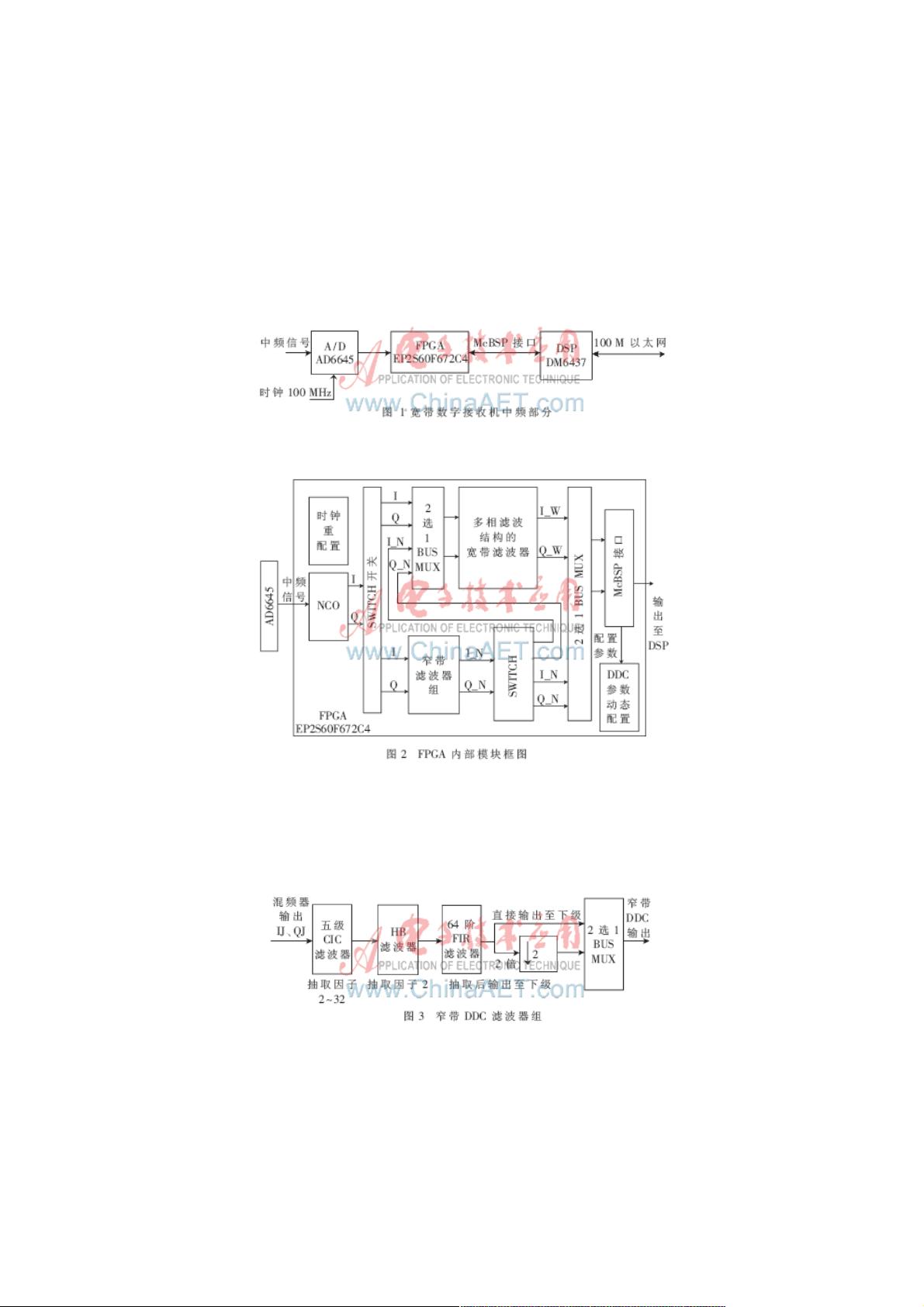

本文主要探讨了一种基于FPGA芯片Stratix II EP2S60F672C4的宽带数字接收机变带宽数字下变频器(VB-DDC)的设计。设计的核心目标是提高宽带数字接收机中频信号的处理效率和灵活性,特别是通过结合传统数字下变频器和多相滤波技术来实现带宽的动态调整。VB-DDC的工作流程包括A/D采样的中频模拟信号输入,经过FPGA内的VB-DDC进行下变频至基带,然后通过McBSP接口传输给DSP进行后续处理,如解调和功率谱估计。上位机PC可以通过McBSP接口配置VB-DDC的参数,实现信号处理带宽的实时调整。

FPGA部分的实现包括两个关键模块:窄带滤波器组和宽带滤波器。窄带滤波器组利用可变滤波器系数和CIC滤波器的抽取因子,能够调整输出数据率在25 MS/s到0.78125 MS/s之间,适应不同信号处理需求。当信号带宽超过1 MHz时,会启用宽带滤波器,设计参数包括通带频率、阻带频率、通带衰减和阻带抑制比,这里使用MATLAB的firpm函数确定了266阶的FIR滤波器设计。为了实现高效的计算,采用了基于多相滤波的乘法器时分复用结构,通过设置多相因子为38和抽取因子为7来优化设计。

数据排序分组采用38个独立的深度为7、位宽为18的FIFO,每个FIFO对应一个多相因子,这使得滤波器的抽取因子可以根据需要在1到7之间变化,从而适应不同信号处理带宽。这种设计方法显著提高了系统的灵活性和处理能力,确保了宽带数字接收机在接收和处理各种宽带信号时都能保持高效和精确。硬件调试的结果证实了该VB-DDC设计的有效性和实用性,这对于现代通信系统,尤其是无线通信和雷达系统,具有重要的实际应用价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-11-05 上传

2021-07-13 上传

2010-05-28 上传

2012-02-19 上传

2021-07-13 上传

2021-07-13 上传

weixin_38743084

- 粉丝: 12

- 资源: 931

最新资源

- CoreOS部署神器:configdrive_creator脚本详解

- 探索CCR-Studio.github.io: JavaScript的前沿实践平台

- RapidMatter:Web企业架构设计即服务应用平台

- 电影数据整合:ETL过程与数据库加载实现

- R语言文本分析工作坊资源库详细介绍

- QML小程序实现风车旋转动画教程

- Magento小部件字段验证扩展功能实现

- Flutter入门项目:my_stock应用程序开发指南

- React项目引导:快速构建、测试与部署

- 利用物联网智能技术提升设备安全

- 软件工程师校招笔试题-编程面试大学完整学习计划

- Node.js跨平台JavaScript运行时环境介绍

- 使用护照js和Google Outh的身份验证器教程

- PHP基础教程:掌握PHP编程语言

- Wheel:Vim/Neovim高效缓冲区管理与导航插件

- 在英特尔NUC5i5RYK上安装并优化Kodi运行环境