高速PCB设计:理论、仿真与EMI抑制解析

需积分: 13 60 浏览量

更新于2024-07-25

收藏 5.23MB PDF 举报

"高速PCB基础理论及仿真技术文档涵盖了信号完整性的基础知识,包括高速数字电路的概述、传输线理论、串扰分析以及EMI抑制等核心内容,旨在帮助理解高速PCB设计中的关键问题和解决策略。"

高速PCB设计涉及到多个关键知识点,首先从基础的信号完整性知识入手。高速电路是指信号频率达到一定阈值,使得信号传输过程中产生的时间延迟和空间分布效应不能忽略的电路。随着电子设备的快速发展,高速电路的设计变得越来越重要。在高速电路中,会出现如信号反射、串扰、电磁干扰(EMI)等问题,这些都可能导致信号失真、系统性能下降甚至设备失效。

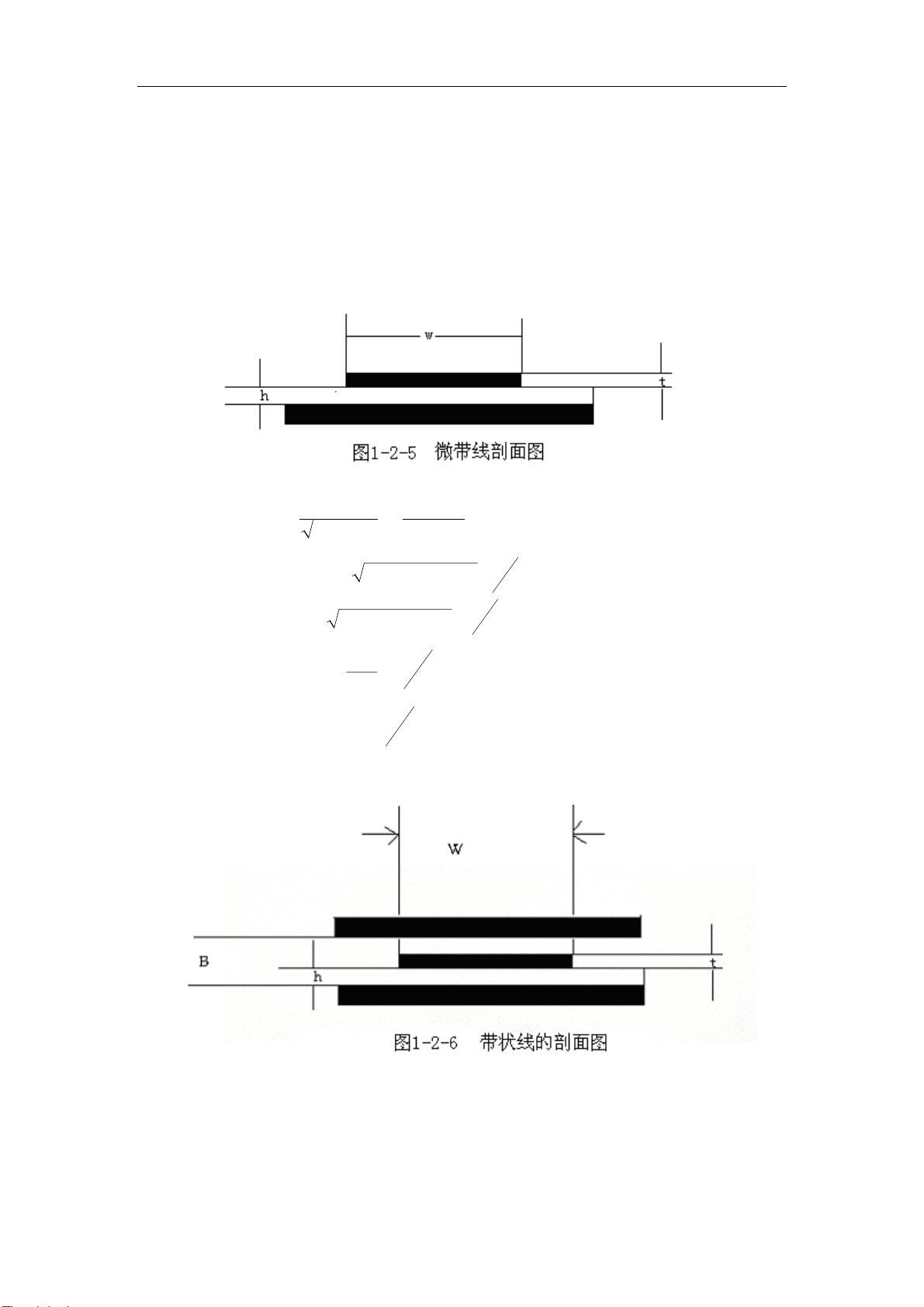

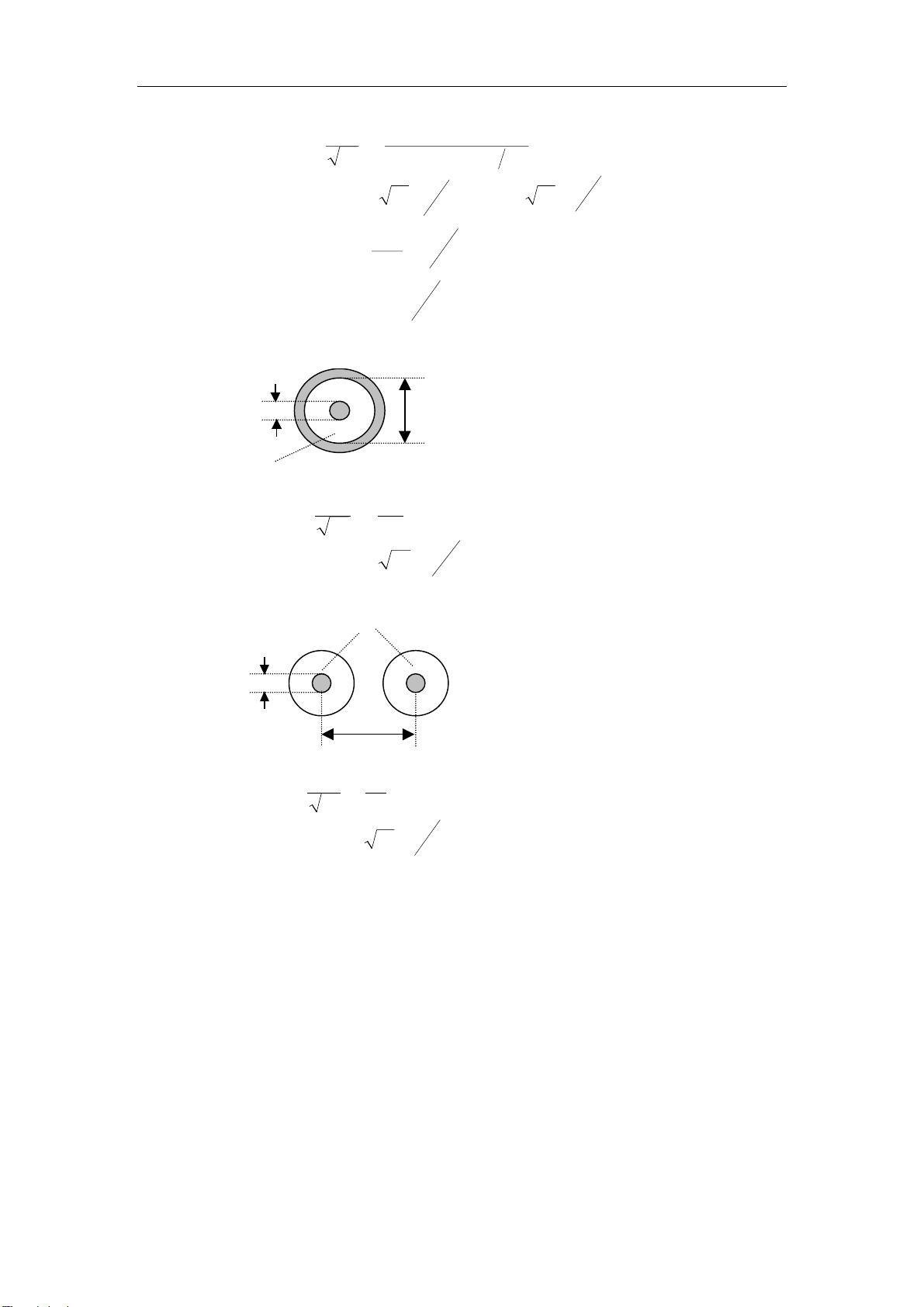

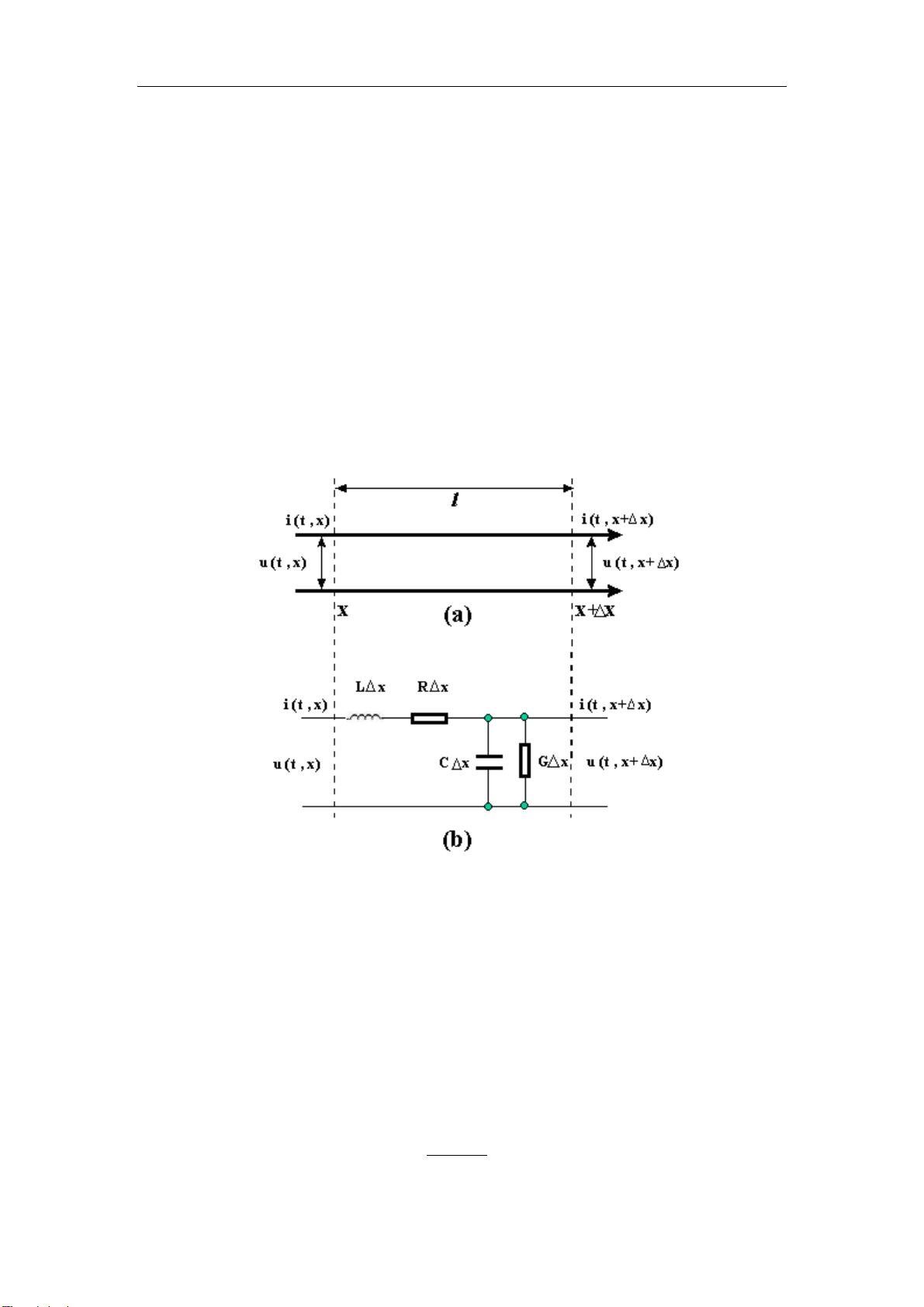

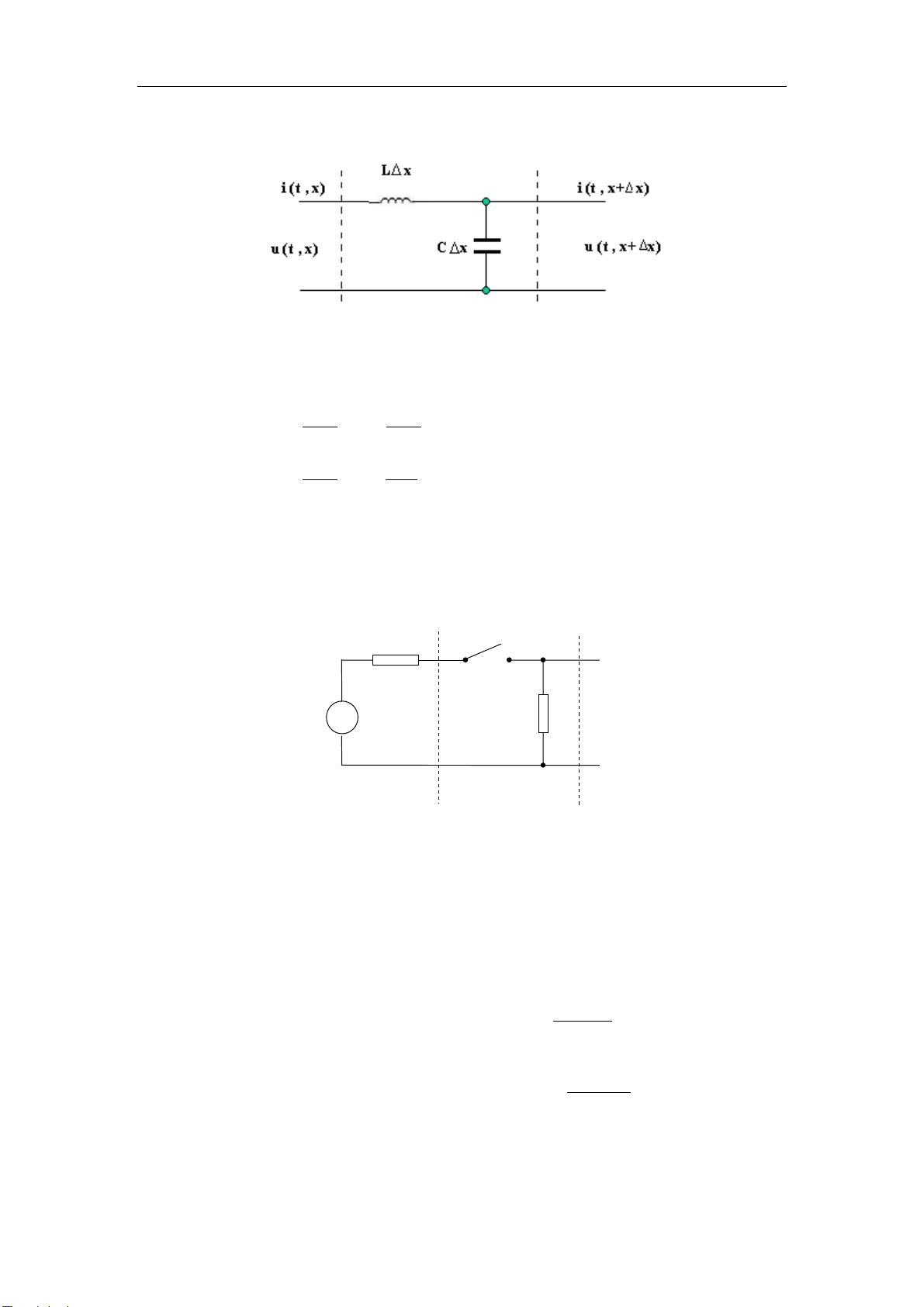

传输线理论是高速PCB设计的基础。传输线是由两根相互平行的导体组成,可以视为一个分布参数的系统,具有电阻(R)、电感(L)、电容(C)和电导(G)。传输线的特性阻抗是其固有属性,它影响着信号在传输过程中的衰减和反射。不匹配的特性阻抗会导致信号反射,引起过冲、下冲和振荡,影响信号质量。反射可以通过串行匹配、并行匹配、差分线匹配以及处理多负载匹配来有效抑制。

串扰是高速PCB设计中的另一个挑战。当相邻的信号线互相靠近时,一个信号线上的电压变化会通过电磁耦合影响到另一个信号线,产生前向串扰和后向串扰。后向串扰可能因为反射而加剧,而串扰的计算涉及共模和差模电流的影响。设计上,可以通过增加间距、使用屏蔽和选择合适的布线策略来减少串扰。

EMI/EMC(电磁干扰/电磁兼容)是高速PCB设计必须考虑的问题。EMI是由于电压瞬变、信号回流和共模、差模电流等因素产生的电磁辐射。为了控制EMI,可以采用屏蔽、滤波和良好的接地设计。屏蔽分为电场屏蔽、磁场屏蔽和电磁场屏蔽,通过选用适当的材料和结构来提高屏蔽效率。滤波则利用去耦电容、磁性元件等降低噪声。在PCB设计阶段,优化传输线的RLC参数和叠层设计也是抑制EMI的重要手段。

内存仿真作为标签提及的内容,可能涉及到内存接口的信号完整性和高速数据传输的模拟。在高速PCB设计中,内存仿真可以帮助设计师预测和分析内存接口的性能,确保数据传输的准确性和稳定性。

高速PCB设计不仅需要理解基础的信号完整性理论,还需要掌握传输线理论、串扰分析和EMI抑制等关键技术,并结合仿真工具进行设计验证,以实现高效、可靠的高速电路系统。

点击了解资源详情

128 浏览量

199 浏览量

2009-07-10 上传

2010-02-21 上传

199 浏览量

点击了解资源详情

点击了解资源详情

2025-02-28 上传

wangqin_88

- 粉丝: 0

最新资源

- 帧中继技术要点与NP帧中继实践笔记分享

- 安装指南:torch_sparse-0.6.12 for Windows with CUDA支持

- Java五子棋游戏代码及其开发心得分享

- Ruby ripl-misc 插件开发:创意与实践

- 深入探讨React与TypeScript的结合应用

- 通信原理课件,易学易懂,考试必备

- Android开发面试题汇总:助你71问高薪无忧

- SSHE项目源码:基于EasyUI和SSH的权限管理框架

- PyTorch Sparse 0.6.12版本兼容指南及安装要求

- 新浪Appkey申请教程:无限制使用指南

- Delphi聊天程序:多人使用界面华丽

- Rebus: Erlang 实现的轻量级 PubSub 事件总线

- Scala编程示例源代码大全

- 大气Excel财务会计简历模板下载

- 加载Milkshape 3D模型与JPEG纹理教程

- GitHub Pages个人网站博客迁移指南:从HTTPS到satharus.github.io