Verilog实现3-8译码器与IP核创建教程

需积分: 19 173 浏览量

更新于2024-07-17

收藏 613KB PDF 举报

该资源主要介绍了如何设计和使用3-8译码器,以及在FPGA中通过Verilog HDL实现,并结合IP核的应用。内容包括多数表决器的设计过程,3-8译码器的Verilog代码实现,以及如何生成和调用IP核。

在电子设计领域,译码器是一种重要的组合逻辑电路,用于将二进制输入信号转换为一组特定的输出信号。3-8译码器是一种能够将3位二进制输入(000到111)解码成8个输出线中的一个为低电平的设备。在描述的资料中,3-8译码器的实现包含了以下几个关键知识点:

1. **多数表决器**:多数表决器是一种逻辑电路,它根据输入信号的多数状态决定输出。在Verilog HDL中,设计了一个多数表决器的源文件,包括代码实现、RTL(寄存器传输级)分析、综合、约束、实现、比特流文件生成、下载和仿真等步骤。

2. **3-8译码器设计**:3-8译码器的实现涉及到了Verilog HDL编程。代码中定义了一个名为v74x138的模块,接收3个使能输入(g1, g2a_l, g2b_l)和3位数据输入(a),并输出8位低有效结果(y_l)。在使能有效的情况下,根据输入a的值,输出相应的解码值;如果使能无效,则所有输出均为高电平。

3. **Verilog HDL代码分析**:代码结构包括模块定义、输入输出声明、内部变量初始化、敏感列表和条件语句。`always @(g1 or g2a_l or g2b_l or a)`表明当这些输入中有任何变化时,代码块内的逻辑将执行。`case`语句用于根据输入a的值设置输出y_l。默认情况下,如果输入无效或未定义,所有输出将为高电平。

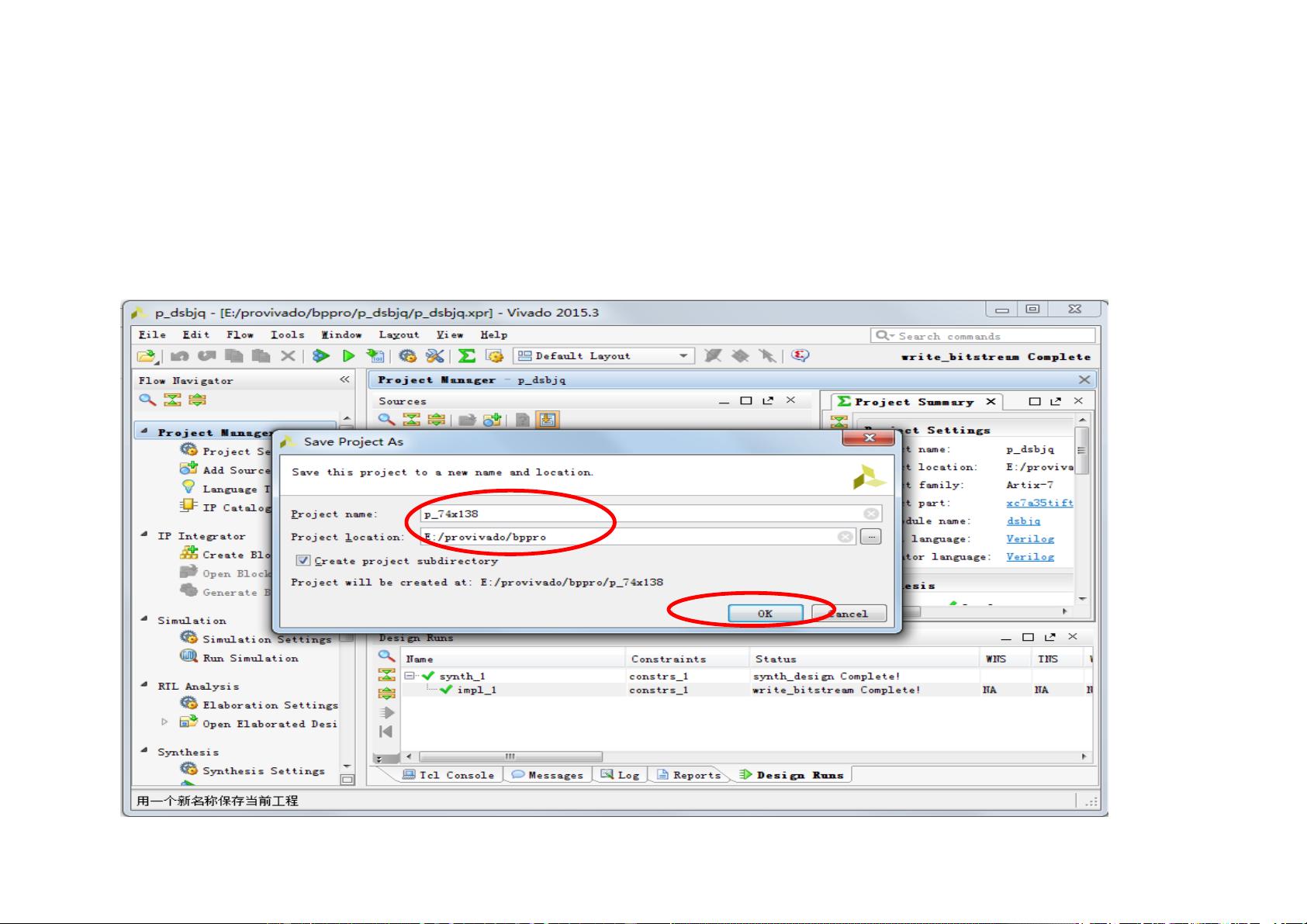

4. **IP核生成与调用**:在设计完成后,可以将工程转化为IP核,以便在其他项目中重复使用。3-8译码器的IP核生成过程包括创建新工程,导入或复制已有的Verilog代码,并进行相应的配置。调用IP核实现多数表决器时,可以使用74x138芯片的逻辑功能,或者直接在新的工程中集成已生成的IP核。

5. **VIVADO进阶**:VIVADO是一款由Xilinx公司提供的基于硬件描述语言的综合工具,支持FPGA设计的全流程,包括设计输入、逻辑综合、布局布线、比特流生成以及硬件下载等。在这个过程中,VIVADO用于管理和驱动整个设计流程,确保设计的正确性和效率。

这份资料提供了一次从理论到实践的完整体验,涵盖了逻辑电路设计的基础知识,Verilog HDL编程技巧,以及FPGA开发中的IP核应用。对于学习和理解数字逻辑设计,尤其是FPGA设计的初学者来说,是非常宝贵的资源。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

pen_swas

- 粉丝: 1

- 资源: 2

最新资源

- PureMVC AS3在Flash中的实践与演示:HelloFlash案例分析

- 掌握Makefile多目标编译与清理操作

- STM32-407芯片定时器控制与系统时钟管理

- 用Appwrite和React开发待办事项应用教程

- 利用深度强化学习开发股票交易代理策略

- 7小时快速入门HTML/CSS及JavaScript基础教程

- CentOS 7上通过Yum安装Percona Server 8.0.21教程

- C语言编程:锻炼计划设计与实现

- Python框架基准线创建与性能测试工具

- 6小时掌握JavaScript基础:深入解析与实例教程

- 专业技能工厂,培养数据科学家的摇篮

- 如何使用pg-dump创建PostgreSQL数据库备份

- 基于信任的移动人群感知招聘机制研究

- 掌握Hadoop:Linux下分布式数据平台的应用教程

- Vue购物中心开发与部署全流程指南

- 在Ubuntu环境下使用NDK-14编译libpng-1.6.40-android静态及动态库