Exar XR16C854/854D:集成128字节FIFO的高性能UART模块

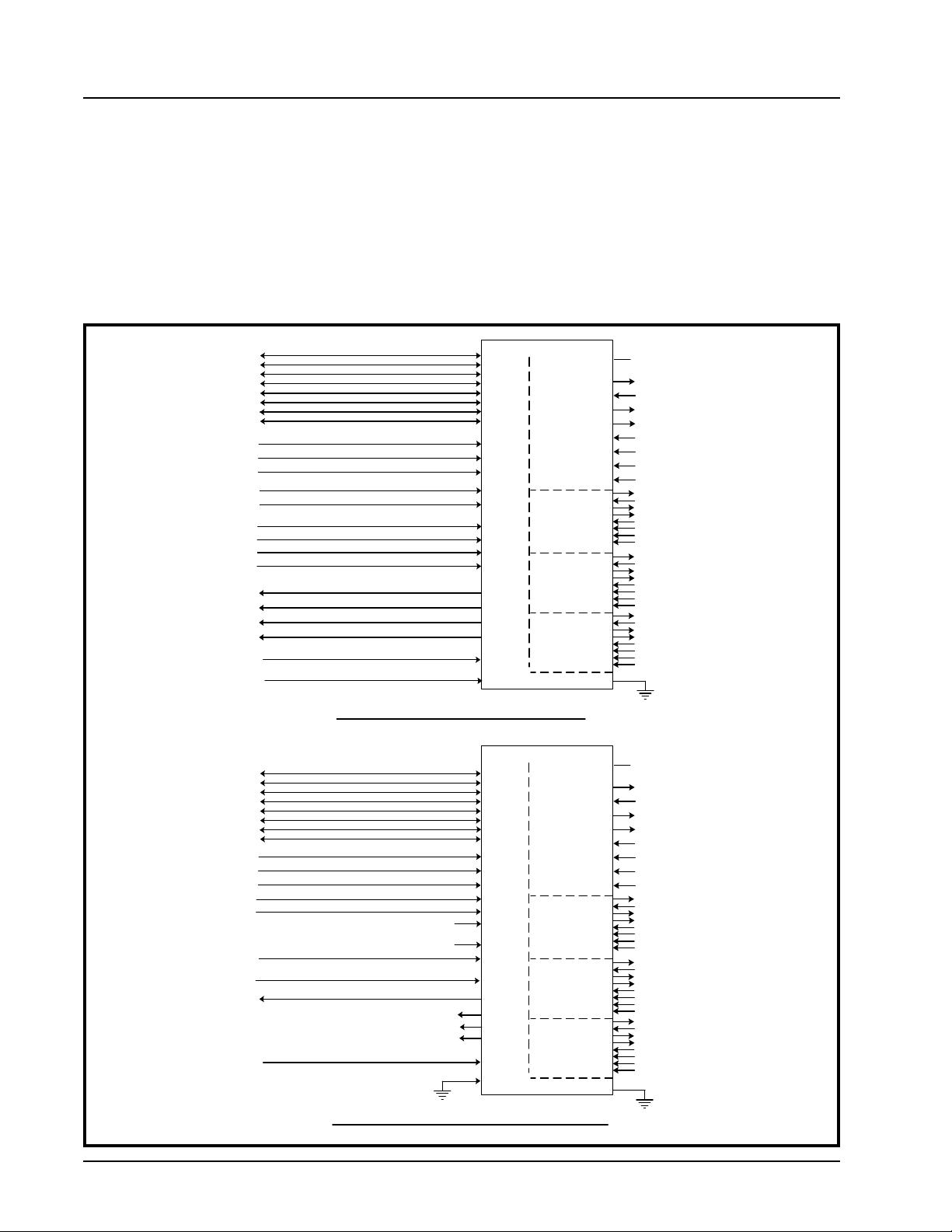

FPGA中的FIFO(First-In-First-Out)功能在数字信号处理和通信系统设计中扮演着重要角色。FPGA,全称为Field-Programmable Gate Array,是一种可编程逻辑器件,它允许用户根据需求灵活地配置电路。在这个案例中,讨论的是Exar Corporation的XR16C854/854D系列芯片,它是一款集成了两个增强型四通道通用异步接收器和发射器(UART)的器件。

每个UART(Universal Asynchronous Receiver and Transmitter)都配备了128字节的发送和接收FIFO(缓冲存储器),这使得数据可以在不中断总线传输的情况下被暂存,从而提高了数据吞吐量和系统的可靠性。FIFO的大小为128字节,意味着它可以存储大量的数据,确保了连续的数据流处理能力,尤其适用于实时通信应用,如串行接口、音频和视频传输等。

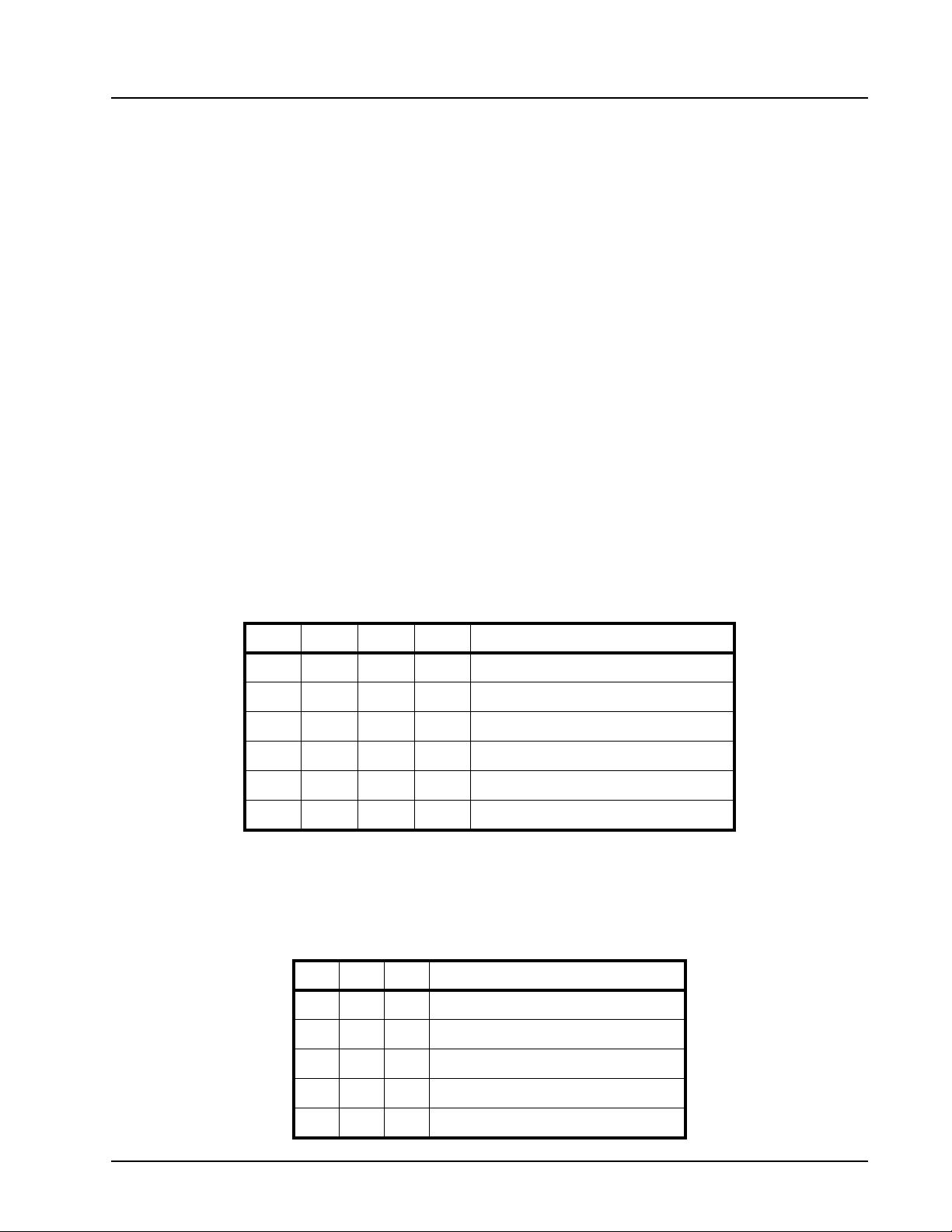

此外,该芯片还具备自动硬件和软件流量控制功能,能够根据设计需求调整数据传输速率,最高可达2Mbps。用户可以通过一组寄存器来监控操作状态、控制功能以及接收错误指示,这提供了对设备运行状况的全面了解和管理。

对于中断处理,XR16C854/854D支持定制的系统中断,便于满足不同设计的需求。内置的环回功能可用于进行板载诊断,验证设备的工作效能。该芯片提供多种封装选项,如64-pin LQFP、68-pin PLCC和100-pin QFP,以适应不同的应用环境和集成度要求。其中,64-pin版本仅支持16位接口,而68-pin和100-pin版本额外提供了68位接口,方便与摩托罗拉处理器的无缝连接。

最后,XR16C854CV型号提供了三态中断输出,这意味着中断信号可以被外部电路直接读取,而XR16C854DV则提供连续的中断输出,这在处理实时中断事件时非常关键。总体来说,FPGA中的FIFO功能是实现高效、可靠数据传输和系统控制的关键组件,适用于多种工业级和消费电子产品的设计。

843 浏览量

254 浏览量

160 浏览量

139 浏览量

点击了解资源详情

点击了解资源详情

333 浏览量

143 浏览量

dawei0302

- 粉丝: 0

- 资源: 1

最新资源

- 作品答辩PPT优质模版.rar

- portfolio-website

- Rcam2:配备LiDAR传感器的iPad Pro远程深度相机

- Nativescript-Template:具有Sidedrawer和Tabview的现代Nativescript-Angular模板

- z-toolz:用于NodeJS开发的工具

- 易语言2D音效

- KOMenuView:简单的可折叠底部菜单

- 【Vue2 + ElementUI】分页el-pagination 封装成公用组件

- zeroexchange-开源

- 无参考代码_无参考图像质量评价_

- sbrunwas.github.io

- nativescript-razorpay:用于nativescript的非官方razorpay插件

- 阅读笔记:读书笔记心得

- MPR New Tab-crx插件

- three-js-meteor:三个带有 Meteor 的 js 动画。 看第四个动画

- mochawesome-report-generator:独立的Mochawesome报告生成器。 只需添加测试数据