Cyclone IV Transceiver详解:硬件与时钟架构设计指南

需积分: 50 33 浏览量

更新于2024-07-17

收藏 4.48MB PDF 举报

本文档是《Quartus Transceiver指南》的一部分,专为Cyclone IV FPGA设计者提供深入的硬件结构和时钟架构详解。Cyclone IV系列是 Altera公司推出的一款高性能FPGA,其Transceiver模块在通信和信号处理应用中扮演关键角色。本文重点介绍的是CYIV-52001-3.7版本,涵盖了Transceiver单元的工作原理、功能特性以及设计注意事项。

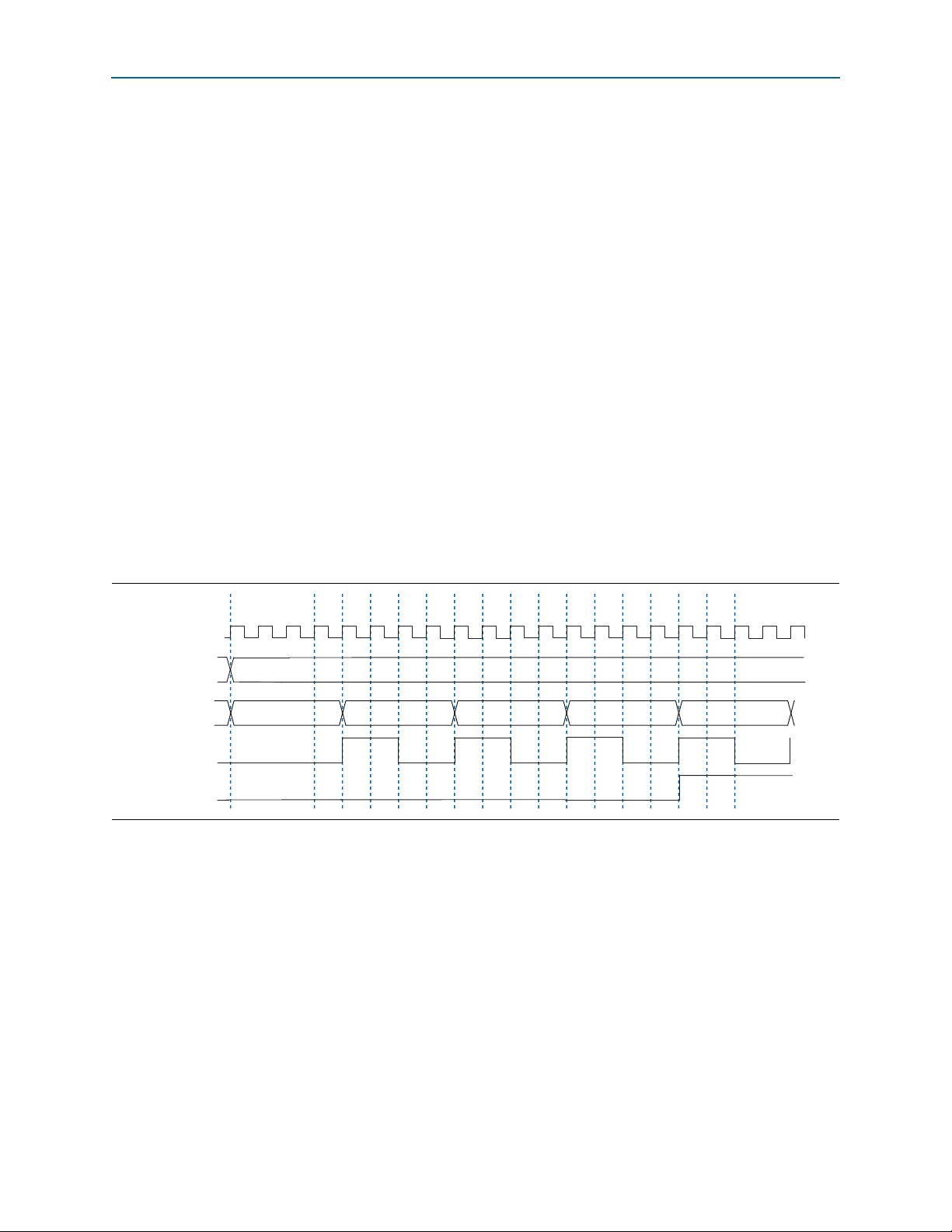

首先,Transceiver在Cyclone IV中负责实现数字与模拟信号之间的转换,包括串行数据的收发、时钟同步以及信号完整性管理。它通常包含物理层接口(PHY)部分,用于处理高速串行通信,如PCIe、USB、LVDS等标准接口,确保数据传输的准确性和可靠性。

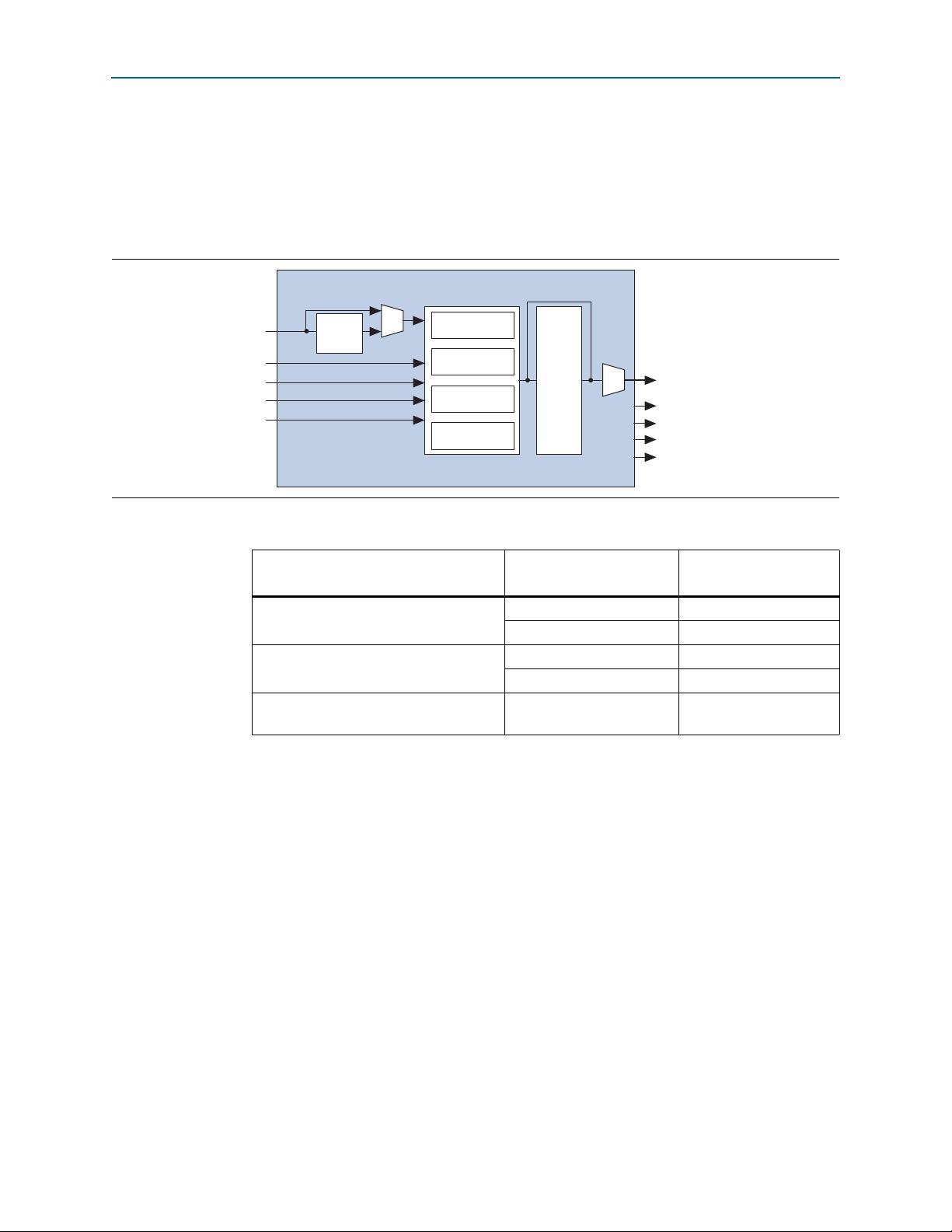

在硬件结构方面,Cyclone IV Transceiver模块由多个组成部分构成,包括数据接收器(Receiver)、数据发送器(Transmitter)、均衡器(Equalizer)、时钟管理单元(Clock Management Block, CMB)以及相关的控制逻辑。接收器负责解码接收到的信号,而发送器则负责编码数据以便于在物理媒介上传输。均衡器用于补偿信号在传输过程中的衰减和噪声,CMB则负责时钟信号的分配和调整,以维持系统内部的同步。

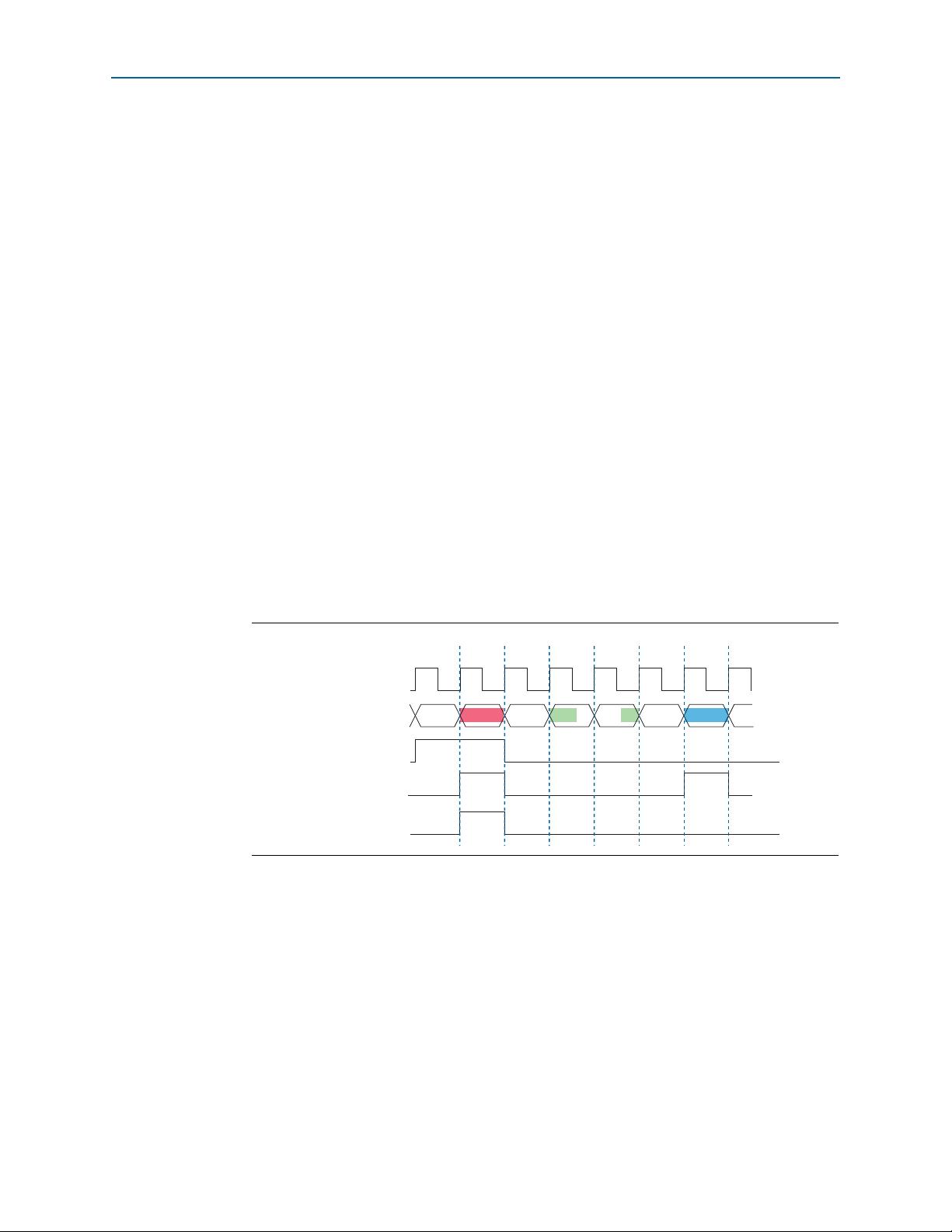

时钟架构对于FPGA的性能至关重要,Cyclone IV Transceiver采用了先进的时钟管理技术,能有效处理多路时钟信号的同步和分发,确保各个逻辑模块间的正确操作。此外,为了满足不同应用场景的需求,可能支持外部时钟输入,以及内部自振荡或锁相环(PLL)机制,以实现灵活的时钟配置。

文档强调,设计者在使用Transceiver前应查阅最新规格,因为Altera会根据技术进步进行产品更新,同时提到了Altera的保修政策,即产品将按照当前规格工作,但在任何时候都保留对产品和服务进行修改的权利。用户在依赖任何信息、产品或服务之前,应确保它们符合最新的设计指南。

最后,文档还标注了ISO 9001:2008的质量管理体系认证,表明 Altera遵循国际质量标准,保证产品的可靠性和一致性。对于寻求优化Cyclone IV Transceiver功能和性能的工程师来说,这份指南提供了宝贵的参考资源,涵盖了从硬件到软件设计的各个方面,有助于提升工程设计的效率和准确性。

2020-08-11 上传

2014-11-06 上传

2017-08-20 上传

2023-12-27 上传

2024-04-13 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

tphayidaa

- 粉丝: 6

- 资源: 8

最新资源

- Proxy-Table-SwiftUI:SwiftUI中的HTTPS代理列表

- ThinkMachine-Advisor:使用ThinkMachine规则的GUI

- java8stream源码-MS-Translator-Speech-HoL:MS-Translator-Speech-HoL

- LiteImgResizer-开源

- 易语言图片修改大小源码.zip易语言项目例子源码下载

- java8集合源码-bookmark:书签

- ARM开发工程师入门宝典.zip

- dgsim:SyncroSim基本软件包,用于模拟野生动物种群的人口统计数据

- TicTacToe

- Gordian Knot-开源

- react-hooks-booklist-tutorial

- 读取excel文件到高级表格.zip易语言项目例子源码下载

- TSC指令大全.rar

- java版商城源码-dev-cheat-sheet:只是一个快速工具和代码片段的汇编,以启动您的开发,主要是针对Web和API。贡献是开放的!

- BounceBall:使用SFML库用C ++编写的简单游戏

- RxSwift-main.zip