Intel Cyclone10 GX收发器PHY全面指南:17.1.1 更新详解

需积分: 0 65 浏览量

更新于2024-06-18

收藏 5.08MB PDF 举报

本指南详细介绍了Intel Cyclone10 GX FPGA收发器物理层(PHY)的相关知识,适用于英特尔Quartus Prime设计套件的更新版本17.1.1。首先,章节1概述了Intel Cyclone10 GX器件收发器的基本结构,包括器件布局、体系架构以及校准过程。器件布局部分介绍了封装细节,收发器由多个Bank构成,每个Bank包含不同的组件如锁相环(PLL)、时钟生成模块(CGB)等。

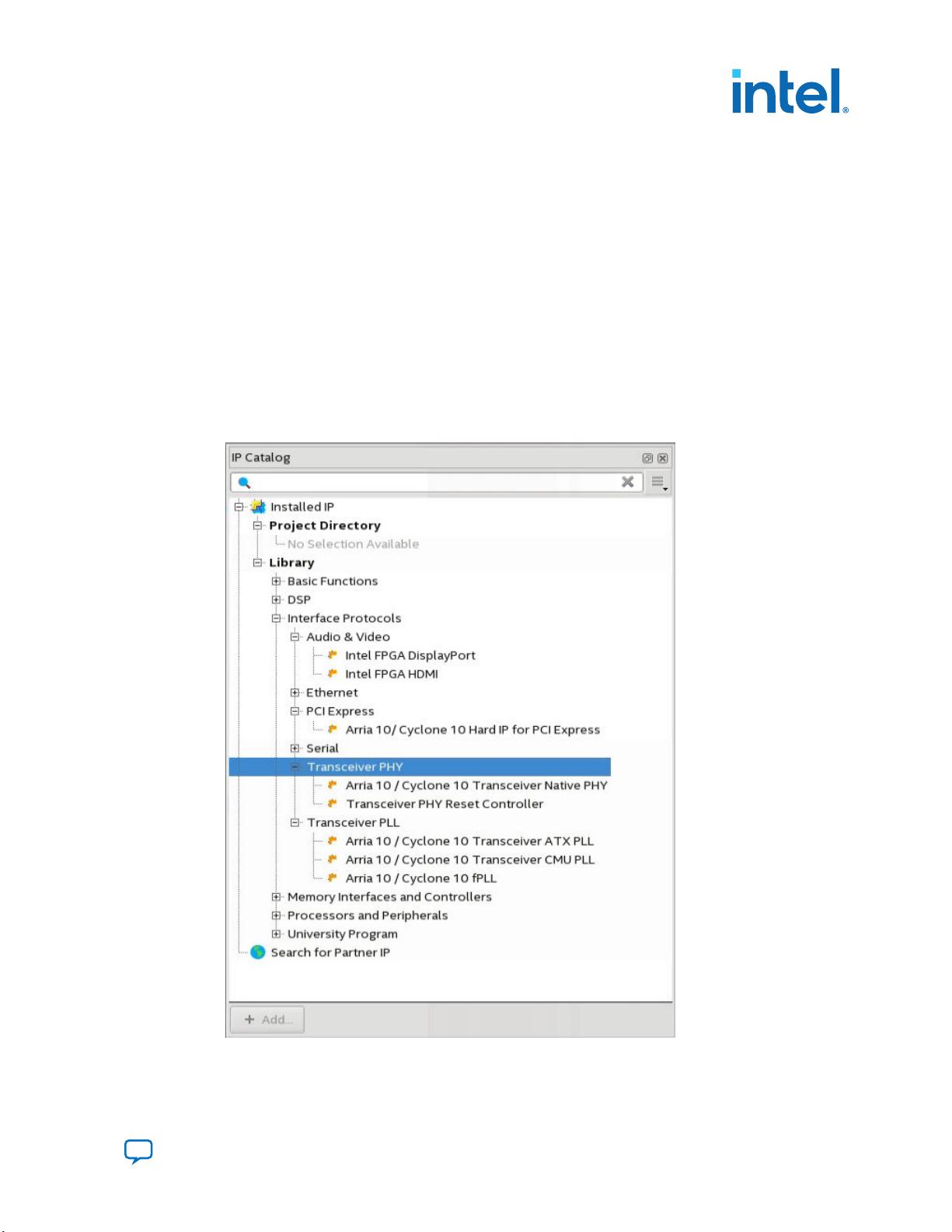

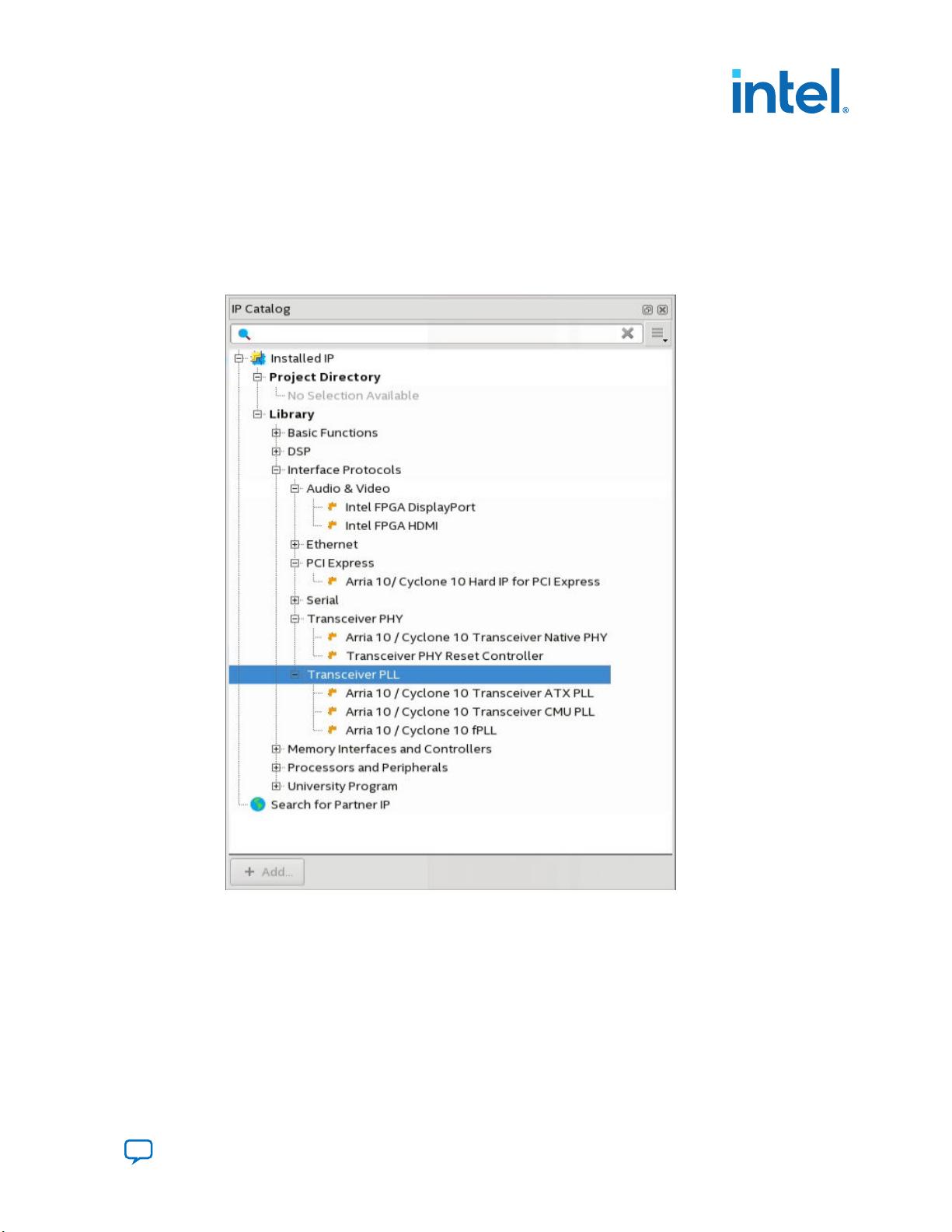

在设计过程中,章节2着重于如何在Cyclone10 GX收发器中实现通信协议。这涉及到使用PHY IP模块,如选择并实例化特定的PHY IP Core,配置其工作模式,包括PLL IP Core的选择和配置,以及复位控制器(ResetController)的集成。设计流程还包括连接数据通路、模拟参数设定、编译和验证设计的功能性。

章节2.4详细讨论了Cyclone10 GX Transceiver Native PHY IP Core的使用,提供了多种参数选项,如预置值、常规参数、PMA(物理媒体接口)参数、增强型PCS(物理链路控制子系统)参数、标准PCS参数、PCSDirect、动态重配置参数和PMA端口设置。这些参数对于定制特定速率、距离和协议规范至关重要。

值得注意的是,这份指南强调了翻译版本仅供参考,建议用户在遇到差异时参考英文原文以获得最新的技术和规格信息。同时,提供了一个联系途径以便用户发送反馈,确保了文档的实时更新和有效性。

该用户指南为Cyclone10 GX FPGA的收发器设计者提供了全面的指导,涵盖了从器件理解、体系结构到实际设计实施的各个环节,旨在帮助用户高效地利用这些硬件资源来构建高性能和可靠的数据通信解决方案。

2021-01-30 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-08-16 上传

FPGAgo

- 粉丝: 46

- 资源: 1

最新资源

- ali-cdn-url:获取阿里云cdn请求地址

- Python3实战Spark大数据分析及调度-第11章 Azkaban实战篇.zip

- 第一个Visual C++应用程序的源码 关于鼠标坐标适时显示

- svelteblox:消费cueblox api的公共网站

- NokiaLCD:诺基亚 5110 LCD 的 AVR 库

- 基于matlab的图像椒盐噪声的平滑效果⽐较

- Latex Documentclass Plan Nacional I+D+i:国家研发计划的LaTeX模板-开源

- Handwritten-Digits-Classification:一种新颖的模型

- VC++ MFC编程实例-新年好

- 6-12-嵌入式省赛.zip

- FriendsFinder:https://enigmatic-taiga-02028.herokuapp.com

- Topic-Constrained-Bodies

- afghanistan-2014-analysis:为我们的阿富汗选举分析托管代码

- hello-world:这是我的第一个仓库

- Webdriver-io-project

- BostonHaskell2015:[Talk] 用 EDSL 构建讨论