Cyclone IV FPGA收发器详细架构与应用指南

需积分: 9 169 浏览量

更新于2024-07-21

收藏 4.52MB PDF 举报

Cyclone IV收发器体系结构是Cyclone IV系列FPGA(Field-Programmable Gate Array)的重要组成部分,它在低成本的数字逻辑芯片上提供了高性能的通信接口功能。该架构专为满足现代应用中的高速串行数据传输需求而设计,包括PCI Express、USB 3.0、SAS和SATA等标准。在CYIV-52001-3.3版本的Cyclone IV器件中,这些内嵌的收发器资源具有显著的优势,如高带宽、低功耗以及灵活的配置选项。

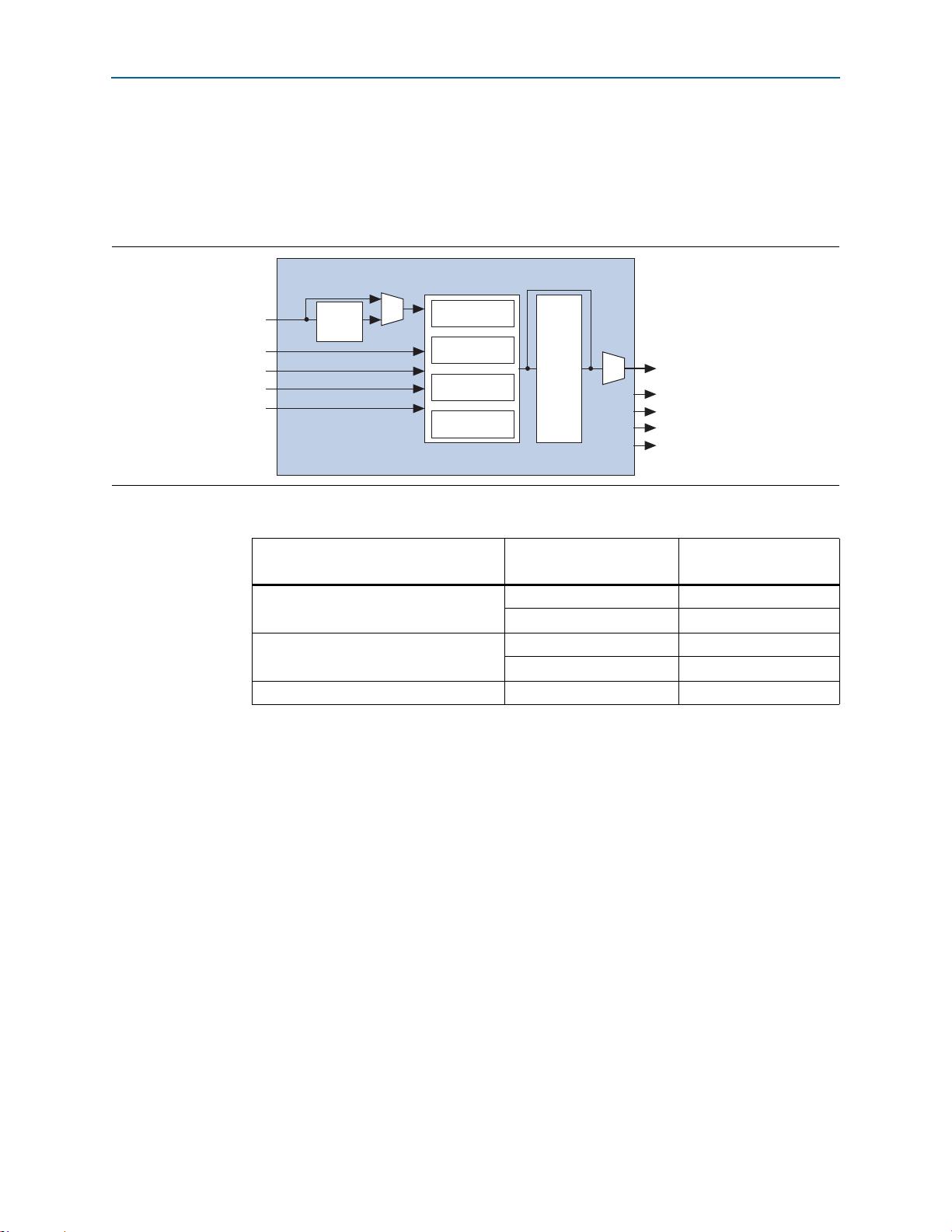

Cyclone IV收发器由以下几个关键部分组成:

1. **基础单元**:收发器模块基于Altera的高级逻辑单元,如查找表(LUTs)、触发器(Flip-Flops)和多路复用器(Multiplexers),这些基本元素提供了构建高速信号处理电路的基础。

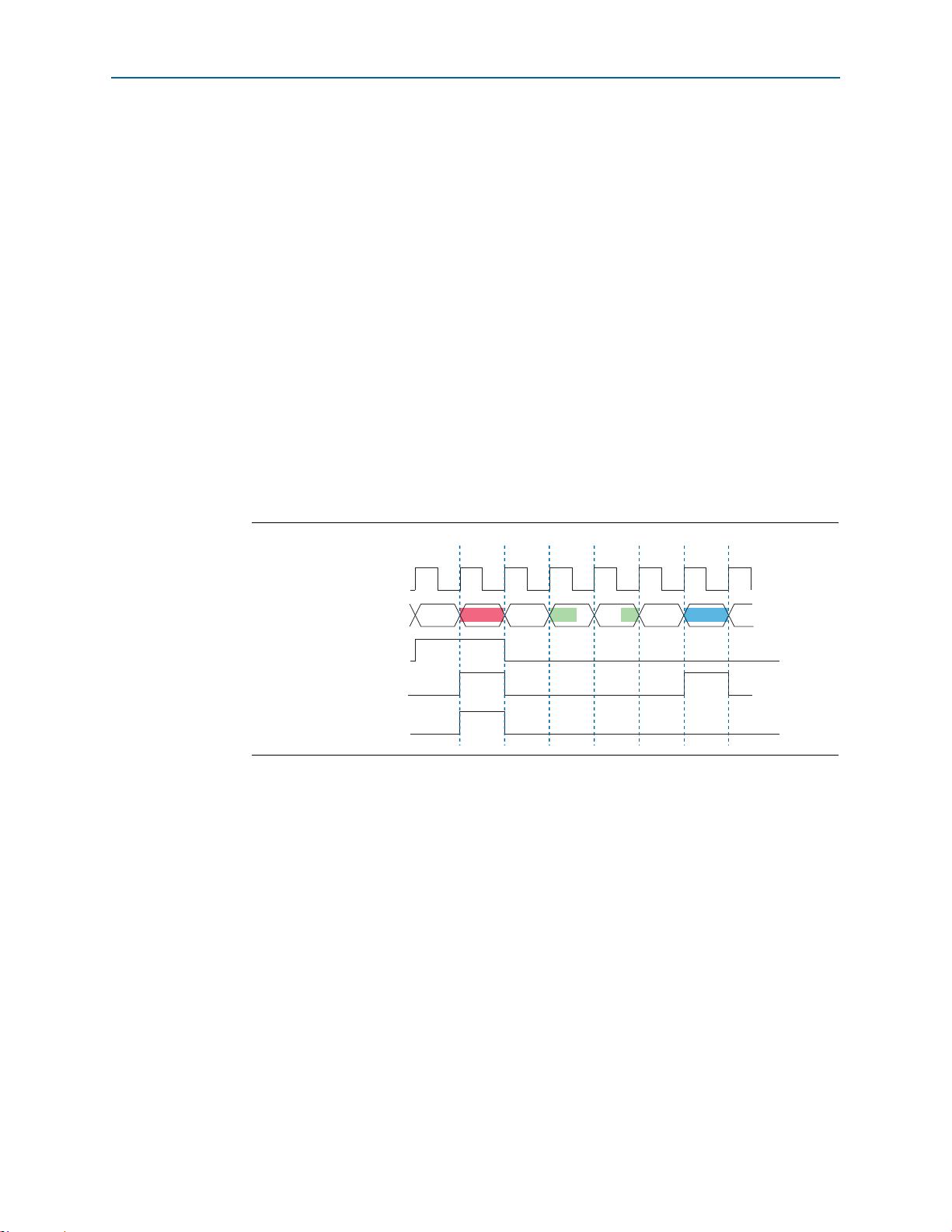

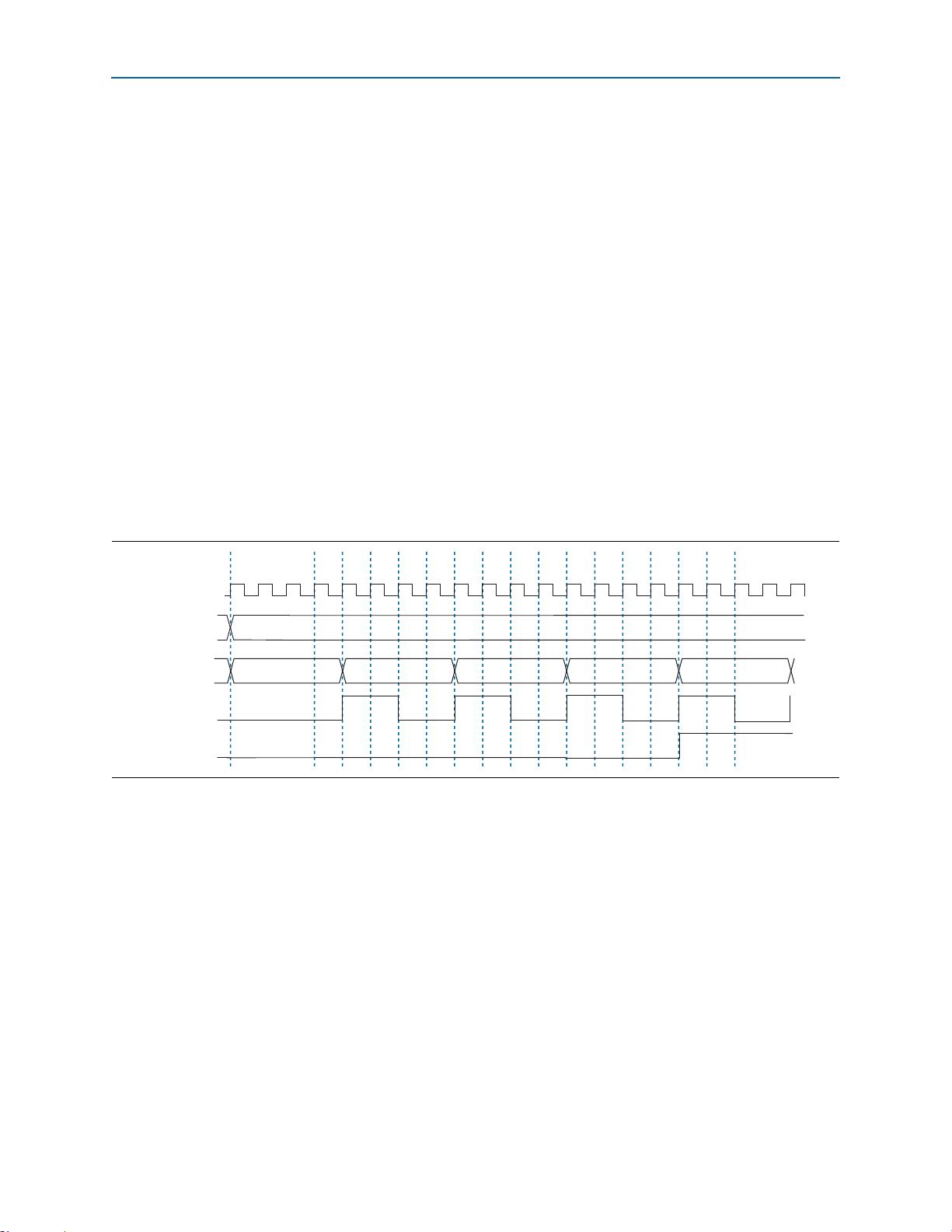

2. **串行/并行转换器**:这些模块允许收发器在串行和并行模式之间切换,以便适应不同的数据传输格式。它们通常包括移位寄存器、锁存器和控制逻辑,用于同步数据流。

3. **时钟管理**:为了确保精确的时钟同步,收发器集成了复杂的时钟分频器、锁相环(PLL)和去抖电路,这对于保持长距离和多级连接的稳定性至关重要。

4. **物理层接口**:包括LVDS(Low-Voltage Differential Signaling)、TTL/CMOS兼容、差分对等接口,支持多种电气标准,如PCIe Gen 2、USB 3.0等,以满足不同应用的需求。

5. **线路驱动和接收器**:高效的电流驱动能力有助于提高信号的强度,防止信号丢失或噪音干扰。同时,精细的接收器设计能够解码复杂的信号格式,确保数据的正确接收。

6. **电源管理和功耗优化**:Cyclone IV收发器针对低功耗设计进行了优化,通过先进的电源管理系统(PMSM)和动态电压调节(DVFS)技术,可以在不影响性能的前提下降低能耗。

7. **配置和管理**:这些器件通常内置了配置闪存,使得用户可以通过JTAG或其他接口方便地下载和更新硬件描述语言(HDL)设计,同时提供监控和诊断功能。

8. **可编程特性**:由于是FPGA架构,收发器的性能可以根据用户的具体应用进行定制和优化,包括但不限于带宽扩展、时序调整、错误检测与纠正等。

Cyclone IV收发器体系结构是实现高效、可靠且灵活的高速接口的关键组件,其在成本效益和性能方面的优秀表现使其成为现代电子系统设计中的理想选择。然而,设计者在使用这些资源时,应始终参考最新的设备规格,并遵循Altera的官方指导,以确保最佳的性能和可靠性。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2018-10-23 上传

2020-10-13 上传

点击了解资源详情

点击了解资源详情

2024-12-25 上传

qq_22255161

- 粉丝: 0

- 资源: 3

最新资源

- Proxy-Table-SwiftUI:SwiftUI中的HTTPS代理列表

- ThinkMachine-Advisor:使用ThinkMachine规则的GUI

- java8stream源码-MS-Translator-Speech-HoL:MS-Translator-Speech-HoL

- LiteImgResizer-开源

- 易语言图片修改大小源码.zip易语言项目例子源码下载

- java8集合源码-bookmark:书签

- ARM开发工程师入门宝典.zip

- dgsim:SyncroSim基本软件包,用于模拟野生动物种群的人口统计数据

- TicTacToe

- Gordian Knot-开源

- react-hooks-booklist-tutorial

- 读取excel文件到高级表格.zip易语言项目例子源码下载

- TSC指令大全.rar

- java版商城源码-dev-cheat-sheet:只是一个快速工具和代码片段的汇编,以启动您的开发,主要是针对Web和API。贡献是开放的!

- BounceBall:使用SFML库用C ++编写的简单游戏

- RxSwift-main.zip