FPGA时序分析与优化技巧

需积分: 12 71 浏览量

更新于2024-09-13

收藏 4.23MB DOCX 举报

"该文档是关于FPGA静态时序分析与优化的总结,主要在Quartus平台上进行讨论。文档涵盖了时序分析的基础概念,如建立时间和保持时间,以及如何处理时序违例问题。作者提供了针对Quartus平台的一些优化建议,包括修改设置和参数、调整代码等方法。"

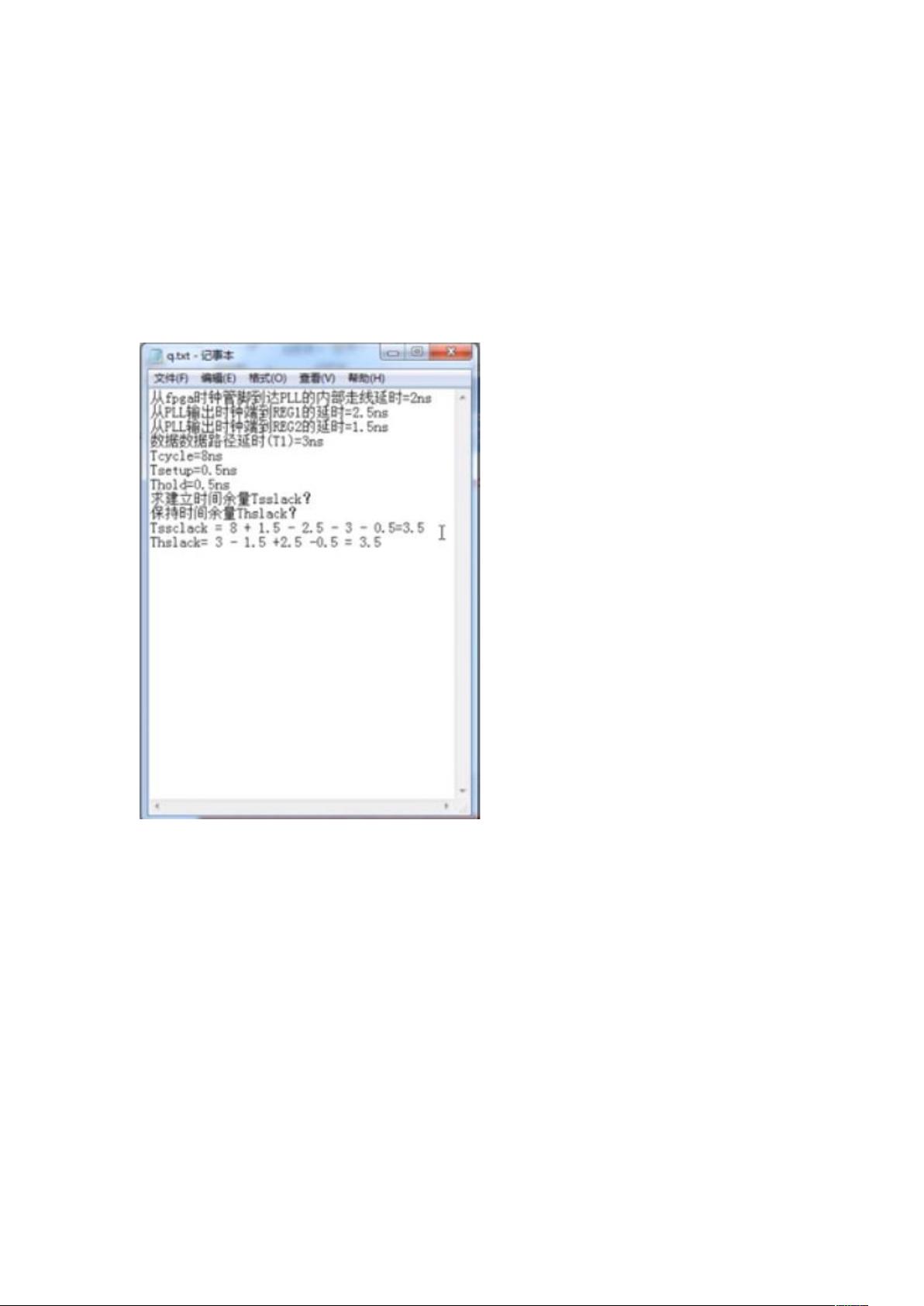

在FPGA设计中,时序分析是确保系统正确运行的关键步骤。时序分析主要关注建立时间和保持时间,这两个参数直接影响着数字系统的可靠性。建立时间(Ts)是指数据需要在时钟边沿到来之前稳定的时间,它由时钟周期(Tc)、时钟偏斜(deltaT)和数据传输延迟(T1)决定。保持时间(Th)则是数据在时钟边沿之后需要保持稳定的时间,它与数据传输延迟和时钟偏斜有关。时序违例通常发生在建立时间或保持时间不足时,可能导致错误的信号采样。

Tslack是衡量是否满足时序要求的关键指标,建立时间余量和保持时间余量分别表示Ts和Th与它们各自的门限值(Tsetup和Thold)之间的差距。理想的时序设计应确保Tslack为正,以防止时序违例的发生。然而,实际设计中,由于器件特性、布局布线和温度变化等因素,Tslack可能会发生变化。

在Quartus这样的FPGA工具中,可以进行静态时序分析以识别并解决这些问题。例如,可以通过改变综合种子数、设置合适的时序优化目标(面积、速度或平衡)来调整设计的时序性能。此外,去除可能影响布局布线的工具,如Signaltap,也可以改善时序。

对于时序违例的处理,有时需要直接修改设计代码。这可能包括在组合逻辑路径中插入额外的寄存器,以减少延迟或打破可能导致长路径的复杂逻辑。特别地,避免在if语句的条件中使用过于复杂的表达式,因为这可能导致数据在多个逻辑单元之间跳动,增加延迟。

FPGA的静态时序分析和优化是一个涉及多方面考虑的过程,包括理解时序参数、合理配置工具设置以及精心调整代码结构。通过这些方法,设计师可以确保设计在高速运行时仍能满足严格的时序约束,从而实现可靠的系统运行。

2019-07-11 上传

2019-10-31 上传

2021-09-14 上传

2023-02-23 上传

2021-10-26 上传

2021-10-26 上传

2021-10-26 上传

2023-09-13 上传

2022-07-09 上传

Arist9612

- 粉丝: 3859

- 资源: 20

最新资源

- C++ Ethernet帧封装_解析_多线程模拟发送消息

- dental-surgery:ASP.NET MVC在牙科手术中的应用

- 美国马里兰大学电池测试数据6:CS2+CX22 (2)

- atom-editor-package:原子游戏引擎的原子编辑器包

- nrraphael.github.io

- golegal:计算围棋中的合法位置数

- AT89C2051+AT24C128+FLEX10K10LC84(Altera的FPGA芯片)+7805+有源时钟组成的原理图

- electricblocks.github.io:电动块的官方网站和文档

- MySQL学习记录,持续更新。.zip

- 客户关系管理

- 基于高斯-拉普拉斯变换LoG算子图像锐化.zip

- StatisticsWorkbook:统计工作簿

- final_proj_sem2:SoftDev第二学期期末项目

- ansible-joyent-inventory:Joyent 的 Ansible 动态库存

- pigfx:PiGFX是Raspberry Pi的裸机内核,它实现了基本的ANSI终端仿真器,并附加了一些原始图形功能的支持

- gmail-force-check:强制 gmail 更频繁地刷新的脚本。 如此处所述