ASIC芯片设计与综合详解

“Advanced ASIC Chip Synthesis”文档主要探讨了ASIC(应用特定集成电路)芯片的高级综合方法,包括设计流程、Synopsys Design Compiler的使用、技术库、逻辑综合过程以及后布局优化等关键步骤。

ASIC设计流程通常涉及以下几个阶段:

1. 验证RTL(寄存器传输级)设计:这是设计流程的起点,确保硬件描述语言(如Verilog或VHDL)的代码正确实现预期功能。

2. 设计约束:设定时序、功耗和面积等目标,这些约束会影响综合和布局布线的结果。

3. IP和库模型:使用预先验证的知识产权(IP)模块和工艺库,以加速设计进程并保证兼容性。

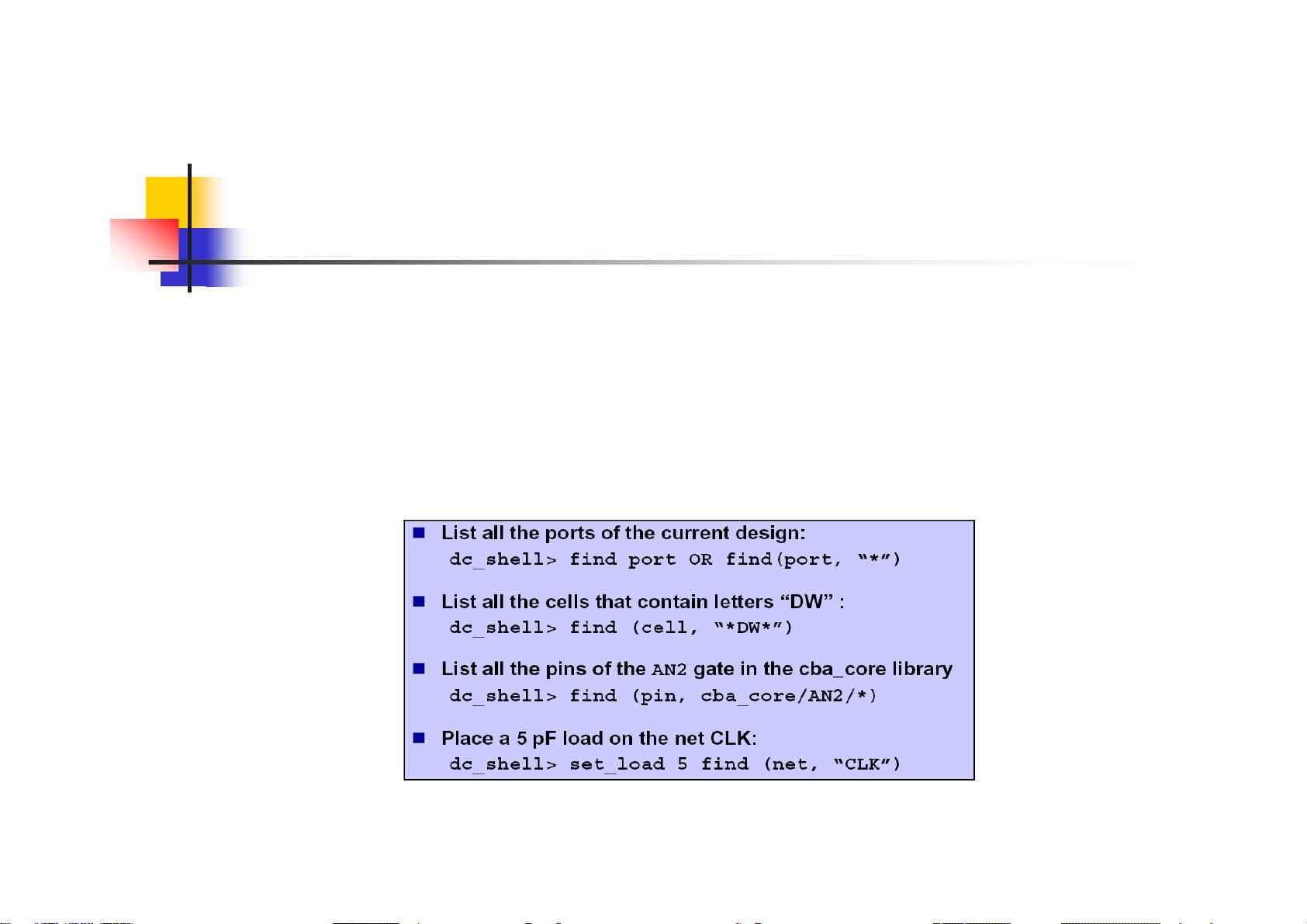

4. 逻辑综合优化与扫描插入:通过Synopsys Design Compiler等工具,将RTL代码转换为门级网表,同时进行逻辑优化和扫描链插入,以提高测试能力。

5. 静态时序分析(STA):检查设计是否满足时序约束,如果不符合,可能需要返回到前面的步骤进行优化。

6. 形式验证:使用形式验证工具确保设计的正确性,避免潜在的逻辑错误。

7. 布局规划、放置与布线:确定芯片上各组件的位置,并连接它们,考虑时序、功耗和面积因素。

8. 时钟树合成:创建时钟网络,确保时钟信号的均匀分布。

9. 后全局路由和后布局优化:进一步优化布线,以改进时序性能。

10. 生成SDF(标准延迟格式)文件:用于描述门级网表中每个门的延迟信息,供后端工具使用。

11. 最终的静态时序分析:在布局布线后再次进行时序检查,确保满足时间约束。

12. 如果时间约束未满足,则需要进行迭代优化,直至满足要求。最终阶段是“Tapeout”,即设计提交给制造厂进行生产。

在描述中提到的示例设计中,一个Tap控制器的实现包含了多个源文件,例如Tap_controller.v、Tap_bypass.v、Tap_instruction.v和Tap_state.v。在完成这些源代码的功能仿真后,设计者将按照上述流程继续进行,包括预布局、逻辑综合、时序分析等步骤,直到满足所有设计要求。

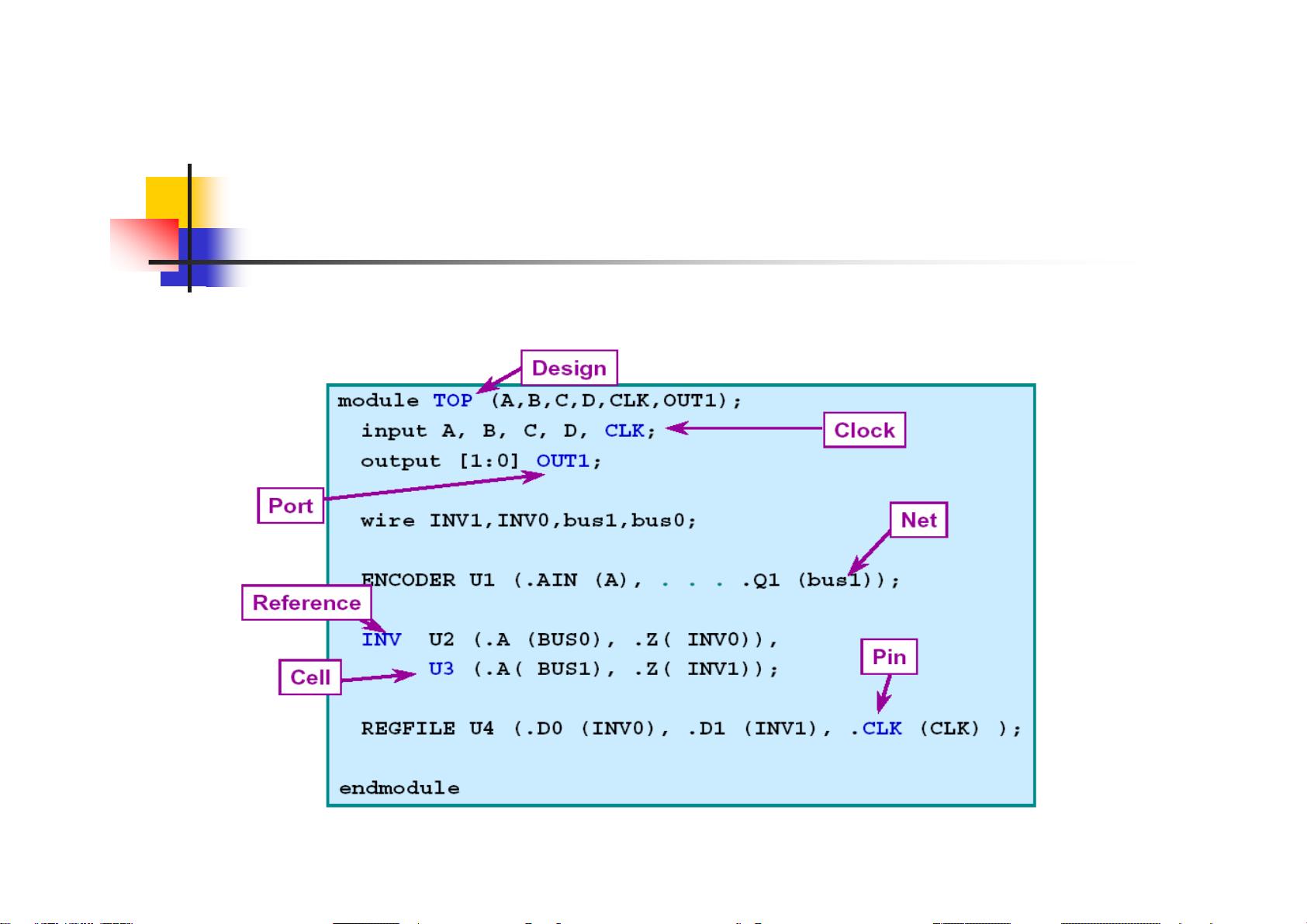

逻辑综合是连接设计逻辑的关键步骤,它将抽象的HDL代码转化为具体的门级表示。在这个过程中,综合工具首先理解HDL代码,生成中间表示(GTECH),然后进行逻辑优化,最后将优化后的逻辑映射到特定工艺库的门级单元中,生成网表。这个过程既要考虑时序性能,又要兼顾面积和功耗,同时还需要增强可测试性,确保设计的可靠性。

点击了解资源详情

108 浏览量

125 浏览量

179 浏览量

256 浏览量

276 浏览量

159 浏览量

136 浏览量

2008-11-26 上传

Cathy_chun

- 粉丝: 0

- 资源: 1