标准单元ASIC设计:前端与后端流程详解

需积分: 50 180 浏览量

更新于2024-07-18

2

收藏 993KB PPT 举报

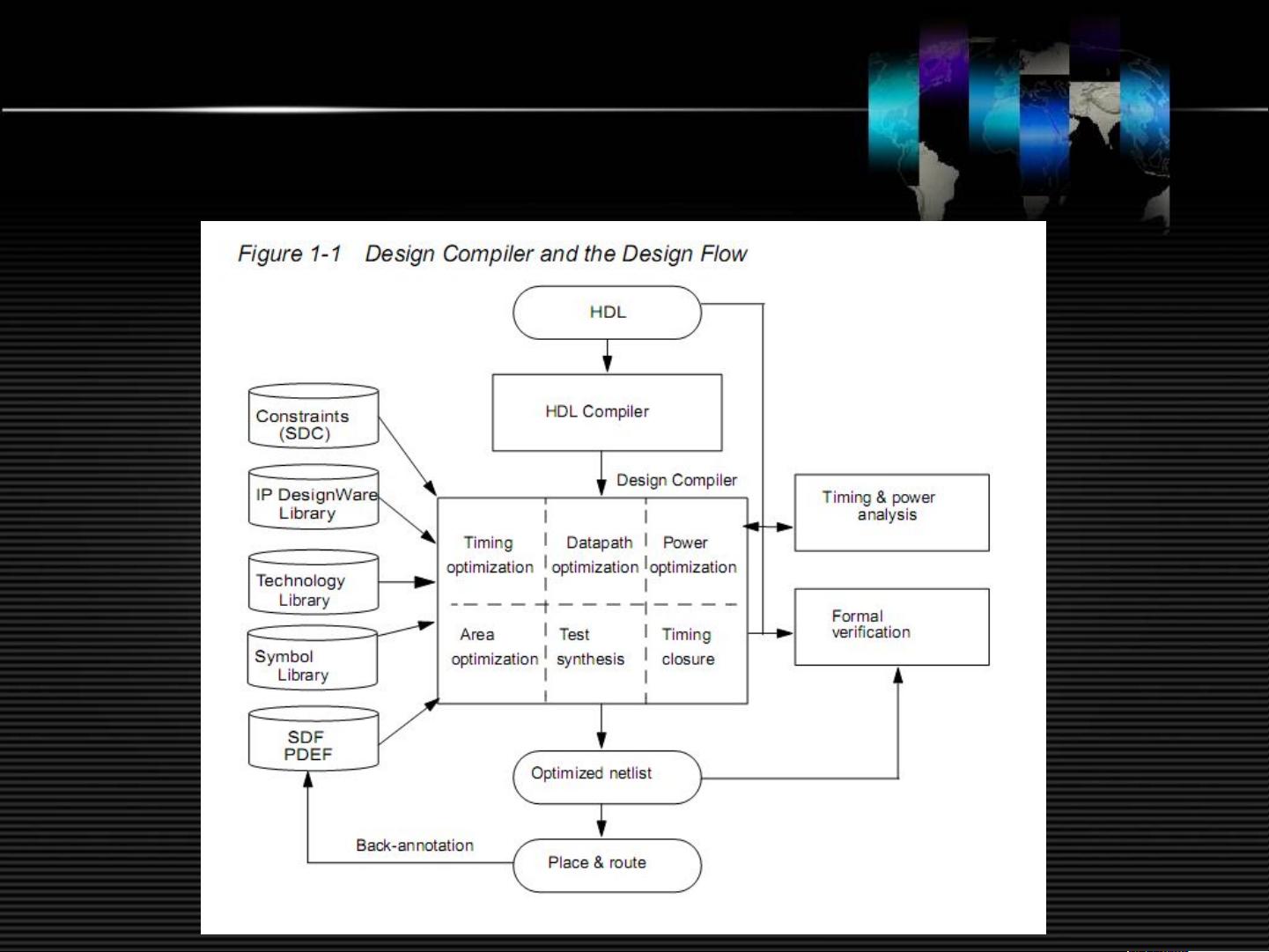

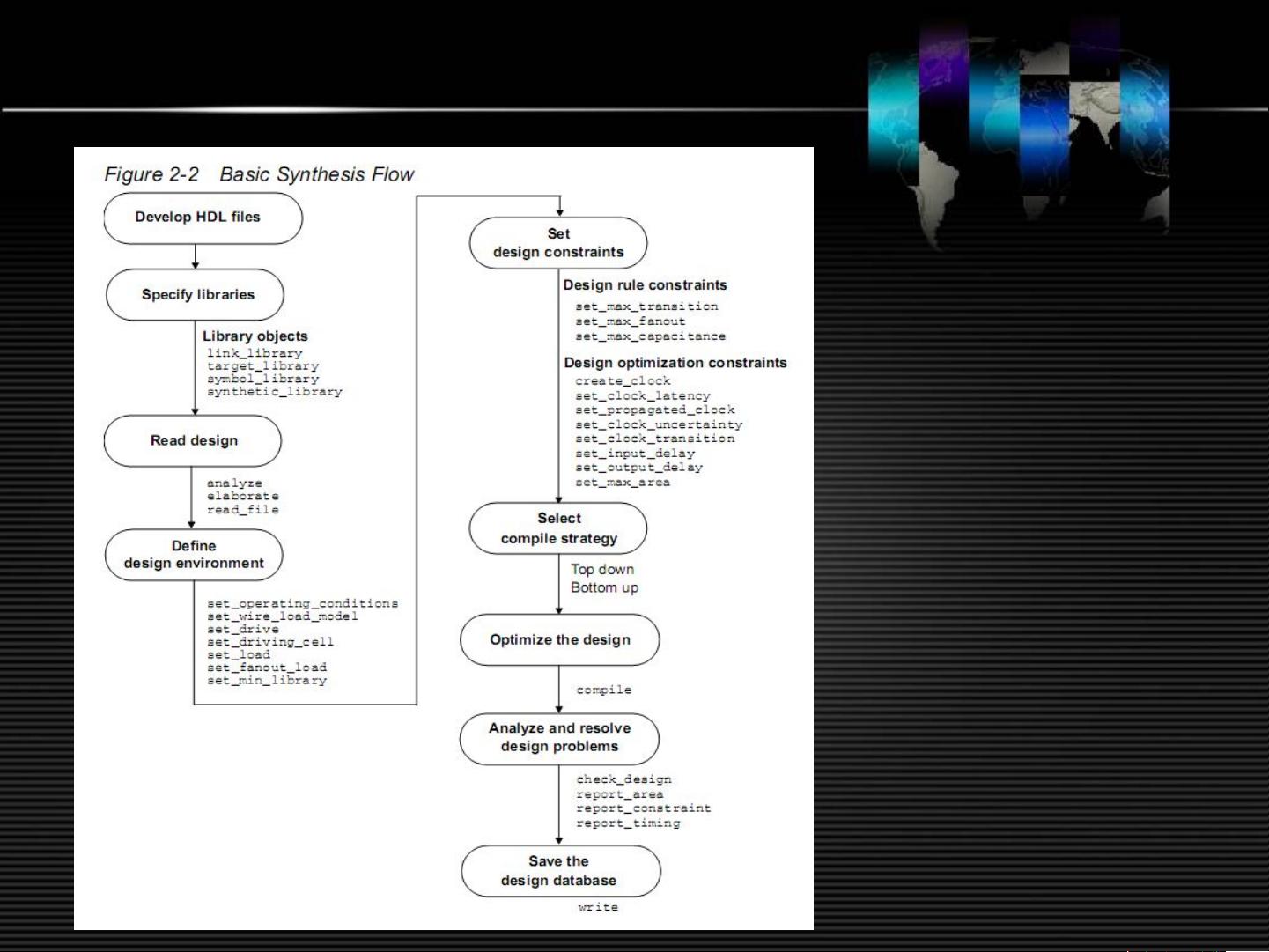

"数字后端流程是一个关键的集成电路设计阶段,特别是在基于标准单元或standcell的ASIC(应用特定集成电路)设计中。它包括了从数字前端设计到最终tape-out的整个过程。以下是对这一流程的详细阐述:

1. 数字前端设计(front-end):此阶段主要关注的是高级设计,例如RTL (Register Transfer Level) 设计,用诸如Verilog或 VHDL这样的硬件描述语言进行描述。设计者会创建算法模型,编写并综合电路行为级的代码,形成NETLIST,这是一种抽象的电路描述。在这个阶段,设计师必须确保设计符合规格要求,可能通过门级仿真来验证其正确性,但这种方法可能耗时且覆盖有限。

2. 综合(synthesis):综合工具将RTL代码转换成电路的具体实现,也就是标准单元或standcell库。工具依据库的功能和时序模型生成电路布局。

3. 静态时序分析:在布局布线前,通常会进行静态时序分析,以检查设计的延迟和满足性能要求的可能性。如果不能满足,可能需要回到前面的步骤进行修改。

4. 布局布线(layout):这是后端设计中的重要环节,使用LAYOUT工具,根据电路单元的时序-几何模型,对电路进行物理布局,生成GDS2文件,这是一种用于制造的详细电路图。

5. 验证(formal verification):除了门级仿真外,形式验证技术也被应用,它通过数学方法全面检查设计的正确性,以弥补门级仿真覆盖率不足的问题。

6. tape-out(提交tape):当所有设计和验证步骤都完成后,设计师会提交最终的GDS2文件给晶圆厂(foundry),如中芯国际,准备进行芯片制造。

在整个流程中,迭代是非常常见的,因为任何阶段的问题都可能导致整个流程的重复或重新设计。数字前端设计的迭代次数可能较多,反映出对精确度和效率的高要求。

数字后端设计工具的选择至关重要,QUATURS II被推荐为参考资源,这表明它可能是业内广泛使用的高效工具之一。同时,教学团队鼓励学生在遇到问题时直接向熟悉相应工具的同学咨询,以便更有效地推进学习和实践。

最后,课程成果是整个DDC项目组的集体智慧结晶,体现了团队合作和持续学习的精神。通过理解并掌握数字后端流程,学生能够更好地为数字IC设计的职业生涯做好准备。"

2651 浏览量

386 浏览量

268 浏览量

574 浏览量

点击了解资源详情

386 浏览量

cfx_id

- 粉丝: 0

最新资源

- Matlab遗传算法工具箱使用指南

- 探索《黑暗王国》:自由编辑的纯文字RPG冒险

- 深入掌握ASP.NET:基础知识、应用实例与开发技巧

- 新型V_2控制策略在Buck变换器中的应用研究

- 多平台手机wap网站模板下载:全面技术项目源码

- 掌握数学建模:32种常规算法深入解析

- 快速启动Angular项目的AMD构建框架:Angular-Require-Kickstart

- 西门子S71200 PLC编程:无需OPC的DB数据读取

- Java Jad反编译器配置教程与运行指南

- SQLiteSpy:探索轻量级数据库管理工具

- VS版本转换工具:实现高至低版本项目迁移

- Vue-Access-Control:实现细粒度前端权限管理

- V_2控制策略下的BUCK变换器建模与优化研究

- 易语言实现的吉普赛读心术源码揭秘

- Fintech Hackathon: 解决HTTP GET私有库文件获取问题

- 手把手教你创建MAYA2008材质库Shader Library