高性能PLL与DDS结合的频率合成器技术探索

193 浏览量

更新于2024-08-28

收藏 1.22MB PDF 举报

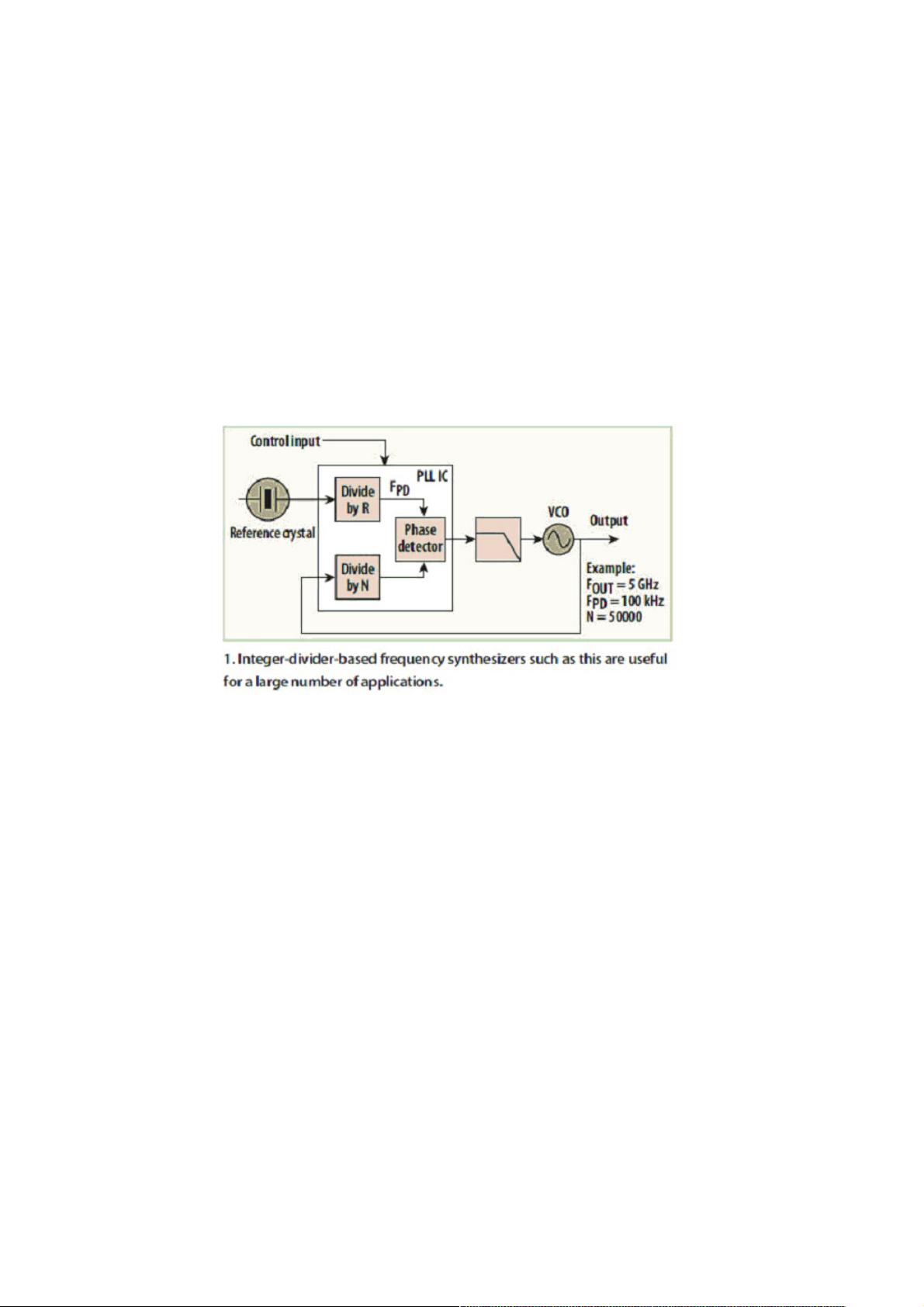

"本文主要探讨了频率合成器的高性能架构实现技术,强调了在面对严格的频率合成器需求时,如何通过灵活设计和采用先进的集成电路来提升性能。文章指出,虽然基本的锁相环(PLL)频率合成器在射频(RF)系统中广泛应用,但在需要高速切换、低相位噪声或低杂散信号的场景下,需要采用更复杂的架构。传统的设计方法包括基于整数分频器或分数N分频器,但可以通过结合使用PLL和直接数字合成器(DDS)来优化性能。文中还提到了压控振荡器(VCO)在实现频率合成中的重要性,并指出VCO的实现方式可以根据具体应用的需求进行选择。此外,高性能设计可能需要考虑制造商的应用笔记,并且可以通过特定的应用程序进行配置。最后,文章提到在一些高要求的应用中,如多普勒雷达和高速通信系统,基本架构可能无法满足相位噪声、杂散信号电平和切换速度等关键指标,需要进一步的技术改进。"

在本文中,我们深入了解了频率合成器的高性能实现策略。锁相环(PLL)作为基本的频率合成手段,具有成本效益高、空间效率好、功耗低的特点,适用于许多RF系统。然而,对于那些需要快速响应、低相位噪声和低杂散信号的系统,PLL可能不足以满足要求。为了提升性能,设计者可能会结合使用 PLL 和直接数字合成器(DDS)。DDS 能提供非常精确的相位控制,而 PLL 可以实现快速频率切换和宽带宽调整,两者结合可以显著改善系统的整体性能。

传统的频率合成器设计通常基于整数分频器或分数N分频器。整数分频器简单且易于实现,而分数N分频器则能提供更精细的频率分辨率。无论采用何种设计,频率合成器IC与外部压控振荡器(VCO)的配合是关键。VCO作为频率合成的核心,其性能直接影响到最终输出信号的质量。VCO的实现方式有多种,可以是集成在IC中,也可以是独立模块或分立元件,根据应用场景的具体需求选择最合适的方案。

高性能设计不仅涉及硬件的选择,还包括软件层面的优化。例如,根据制造商提供的应用笔记进行设计,利用专用应用程序来配置合成器的寄存器加载和调整相位检测器增益,以达到最佳性能。对于那些要求极其严苛的应用,如多普勒雷达系统和采用快速频率切换及高阶调制的通信系统,基本的PLL架构可能无法达到理想的相位噪声、杂散信号电平和切换速度,此时需要对架构进行深度定制和改进。

频率合成器的高性能架构实现技术是一项综合了硬件选型、系统设计和软件配置的复杂任务。通过创新的设计思路,结合现代集成电路技术,可以实现满足各种苛刻需求的频率合成器,以适应不断发展的无线通信和雷达技术。

2020-10-19 上传

2024-03-12 上传

点击了解资源详情

点击了解资源详情

2020-07-31 上传

2021-07-12 上传

2021-07-12 上传

2021-07-13 上传

2021-07-13 上传

weixin_38592455

- 粉丝: 7

- 资源: 896

最新资源

- NIST REFPROP问题反馈与解决方案存储库

- 掌握LeetCode习题的系统开源答案

- ctop:实现汉字按首字母拼音分类排序的PHP工具

- 微信小程序课程学习——投资融资类产品说明

- Matlab犯罪模拟器开发:探索《当蛮力失败》犯罪惩罚模型

- Java网上招聘系统实战项目源码及部署教程

- OneSky APIPHP5库:PHP5.1及以上版本的API集成

- 实时监控MySQL导入进度的bash脚本技巧

- 使用MATLAB开发交流电压脉冲生成控制系统

- ESP32安全OTA更新:原生API与WebSocket加密传输

- Sonic-Sharp: 基于《刺猬索尼克》的开源C#游戏引擎

- Java文章发布系统源码及部署教程

- CQUPT Python课程代码资源完整分享

- 易语言实现获取目录尺寸的Scripting.FileSystemObject对象方法

- Excel宾果卡生成器:自定义和打印多张卡片

- 使用HALCON实现图像二维码自动读取与解码