高性能频率合成器架构: PLL与DDS的融合技术

57 浏览量

更新于2024-08-31

收藏 287KB PDF 举报

"基础电子中的频率合成器的高性能架构实现技术"

在电子工程中,频率合成器是关键组件,尤其在射频(RF)系统中,它负责生成精确、可调的频率源。本文主要探讨了如何实现满足严格要求的高性能频率合成器架构,特别是针对那些需要快速切换速度、低相位噪声和低杂散信号的应用。

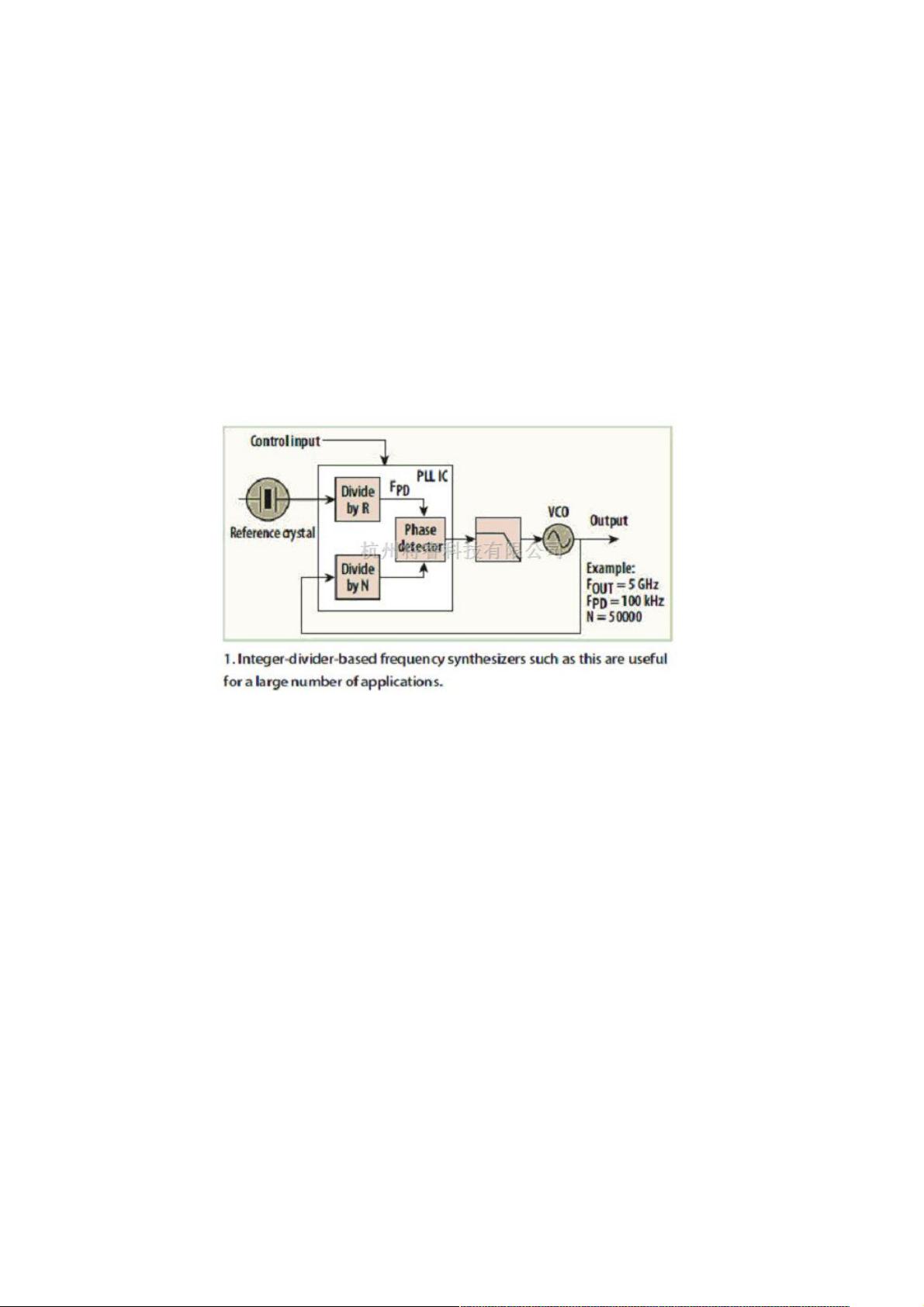

首先,基础的锁相环(PLL)频率合成器是一种常用的技术,它以低成本、高效空间利用和低功耗著称,能够提供良好的频谱纯度和频率跳变能力。PLL的工作原理是通过调节压控振荡器(VCO)的频率,使其与参考信号保持相位同步,从而产生所需的输出频率。然而,对于某些高要求的应用,简单的PLL架构可能无法满足性能需求。

为了提升性能,设计者可能会采用更复杂的架构,比如结合使用PLL和直接数字合成器(DDS)。DDS是一种数字技术,可以直接生成任意频率的正弦波,具有出色的相位控制和低相位噪声特性。将DDS与PLL集成可以实现快速频率切换,因为DDS可以快速改变其输出相位,而PLL则用于稳定频率并减少相位噪声。这样的组合架构可以兼顾频率精度、切换速度和低噪声性能。

在设计过程中,分频器的选择也至关重要。传统的频率合成器常使用整数分频器或分数N分频器。整数分频器简单且易于实现,但可能导致较大的调谐步长和相位噪声;而分数N分频器则可以提供更精细的频率分辨率,但设计上更为复杂。根据应用的具体需求,如频率范围、相位噪声要求、空间限制、成本和功耗等因素,可以选择合适的分频器类型。

集成的频率合成器IC通常包含了PLL和分频器的核心功能,可以简化系统设计,并可能包含VCO。VCO的选择和设计直接影响频率合成器的性能,包括相位噪声、杂散信号和频率响应。对于特定应用,可能需要在IC、模块或分立元件之间进行选择,以满足特定的频率范围和噪声性能。

此外,应用程序支持是实现高性能频率合成器的关键环节。制造商通常会提供应用笔记和软件工具,帮助用户配置合成器的寄存器,调整相位检测器增益等参数,以优化系统性能。

对于那些需要极高性能的应用,如多普勒雷达系统和高速通信设备,基本的PLL和DDS架构可能需要进一步优化。例如,当需要在高输出频率下保持小的调谐步长时,会导致大的分频比,从而增加环路带宽内的相位噪声。在这种情况下,可能需要采用更高级的滤波技术、优化的VCO设计或者采用混合信号技术来降低相位噪声和杂散信号。

实现高性能的频率合成器架构涉及到多方面的考虑,包括选择合适的PLL和DDS IC、分频器类型、VCO设计,以及利用制造商提供的工具进行参数优化。设计师必须根据具体应用的性能指标,如相位噪声、切换速度和杂散信号,来权衡这些因素,以构建满足需求的高效能频率合成器。

2021-01-20 上传

2024-03-12 上传

2020-07-31 上传

2021-07-12 上传

2021-07-12 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

weixin_38637665

- 粉丝: 4

- 资源: 951

最新资源

- 天池大数据比赛:伪造人脸图像检测技术

- ADS1118数据手册中英文版合集

- Laravel 4/5包增强Eloquent模型本地化功能

- UCOSII 2.91版成功移植至STM8L平台

- 蓝色细线风格的PPT鱼骨图设计

- 基于Python的抖音舆情数据可视化分析系统

- C语言双人版游戏设计:别踩白块儿

- 创新色彩搭配的PPT鱼骨图设计展示

- SPICE公共代码库:综合资源管理

- 大气蓝灰配色PPT鱼骨图设计技巧

- 绿色风格四原因分析PPT鱼骨图设计

- 恺撒密码:古老而经典的替换加密技术解析

- C语言超市管理系统课程设计详细解析

- 深入分析:黑色因素的PPT鱼骨图应用

- 创新彩色圆点PPT鱼骨图制作与分析

- C语言课程设计:吃逗游戏源码分享