CPLD为核心的数字电压表设计:高精度与自动量程转换

141 浏览量

更新于2024-08-31

收藏 332KB PDF 举报

"一种以CPLD为核心处理电路的数字电压表设计"

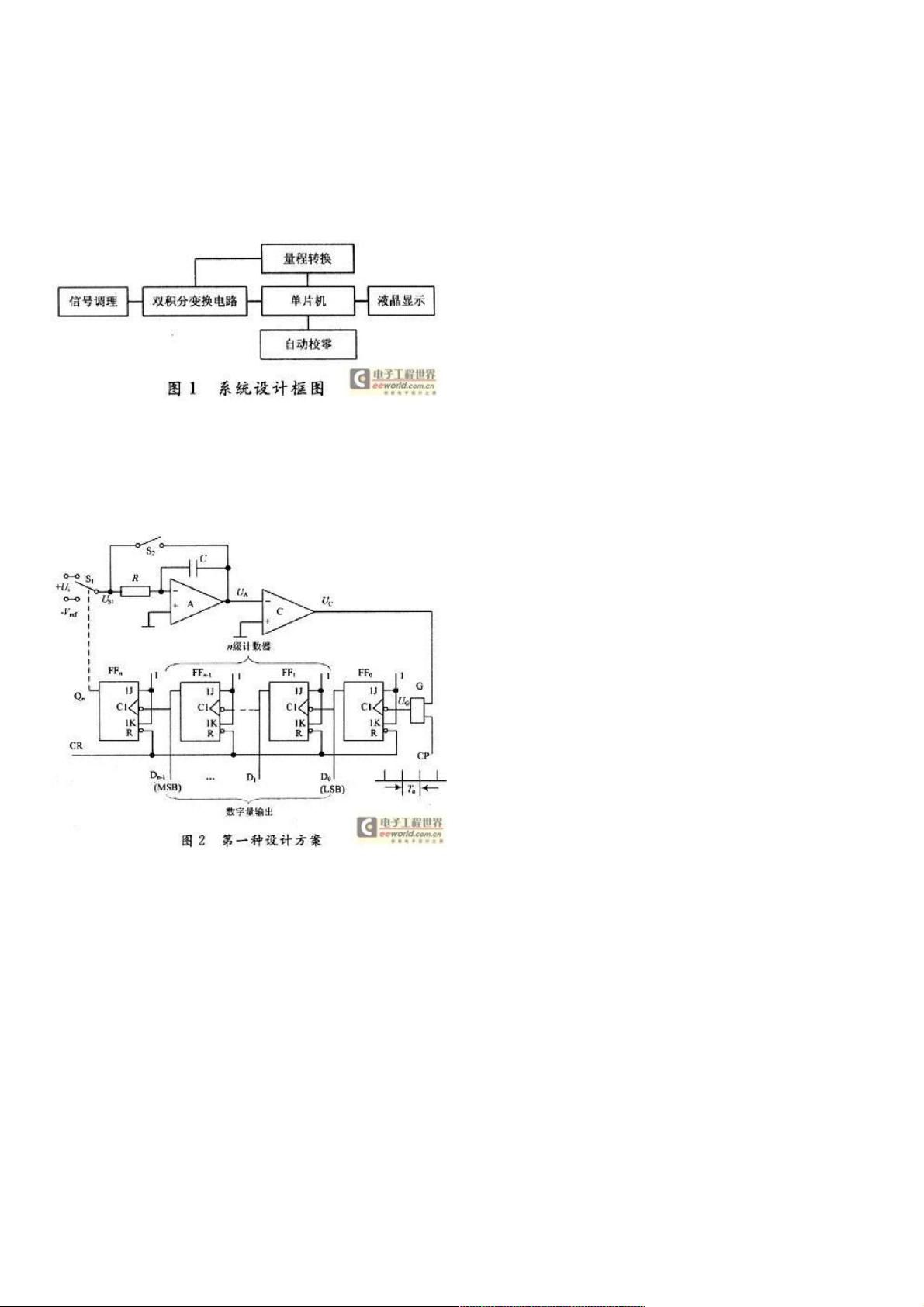

本文介绍了一种以CPLD(复杂可编程逻辑器件)为核心的数字电压表设计,该设计利用CPLD的强大逻辑处理能力,配合单片机进行控制,提高了电压表的抗干扰能力和分辨率。数字电压表的一个关键特性是其能自动切换量程,从而提升了测量的精确度和适应性。

在方案论证与比较阶段,文章提出了两种设计方案。第一种方案是使用J-K触发器构建二进制异步加法计数器,但这种方法会因为触发器数量多而占用较大空间,且容易受到干扰。相比之下,第二种方案采用了CPLD,它将16位J-K触发器和控制电路集成在一起,不仅能减少外界干扰,还能节省空间并提高响应速度,因此被选为最终设计方案。

在系统设计部分,硬件部分的详细设计包括:

1. 滤波电路:采用压控二阶低通滤波器,由运算放大器OP07和电容电阻网络组成,设计中通过调整参数实现了10Hz的截止频率,以过滤掉高频噪声。

2. 测量放大器:使用了AD620仪表放大器,通过8选1模拟开关CD4051选择不同的增益值,适应不同量程的电压测量,确保了从0.1mV到2V的宽范围测量。

3. 双积分转换电路:由积分器和检零比较器组成,积分器对输入电压和基准电压进行积分,检零比较器用于判断积分结束,CPLD在此环节中起到了控制计数器的作用,记录积分过程的时间,从而转化为电压值。

CPLD器件EPM7128在系统中的角色至关重要,它不仅提供了门控开关、计数器、数据寄存器和辅助触发器等功能,还内置了存储器,无需额外的外部组件。这种集成化的设计使得整个系统更加紧凑,减少了外部干扰的可能性,提高了系统的稳定性和精度。

这种基于CPLD的数字电压表设计优化了传统的电压表结构,通过CPLD的高度可编程性实现了复杂的逻辑控制,提升了电压测量的性能,特别是在抗干扰和分辨率方面表现出色。同时,通过自动量程转换,确保了在不同电压范围内的准确测量,是现代电子测量领域的一个创新应用。

2009-07-30 上传

107 浏览量

101 浏览量

221 浏览量

105 浏览量

162 浏览量

2015-12-16 上传

2022-11-28 上传

2022-11-28 上传

weixin_38557757

- 粉丝: 5

- 资源: 934

最新资源

- go-jsonfeed:Go包,用于解析和构建JSON Feed

- protractor-angularjs-test-example-2:使用量角器对 AngularJS 进行端到端测试的示例

- 首次测试:esto es una practica

- 美食博客动态响应式网站模板

- 含系统签名*.jks的Android系统签名的Windows和Linux方法教程

- csharp-project--web-application-:GPS系统的最后一年项目

- Base-MeteorBox:使用 vagrant 设置流星项目的基本流星盒,这是使用 macOSx 和 VirtualBox 完成的

- Desktop.zip

- react-basic:刷新React的基础知识

- 左右滚动日志动态响应式网页模板

- openwrt-lede

- epicodus-ember-epinions

- nodeboilerplate

- GreatDJ-crx插件

- VideoLive-master.zip

- 网络游戏-基于演化混沌量子神经网络的最优多用户检测方法.zip