富士电机FRENIC-VG变频器操作与维护手册

需积分: 5 13 浏览量

更新于2024-07-17

收藏 3.54MB PDF 举报

"富士变频器FRENIC-VG系列的使用说明书,涵盖了该高性能矢量控制型变频器的参数设置和安全注意事项"

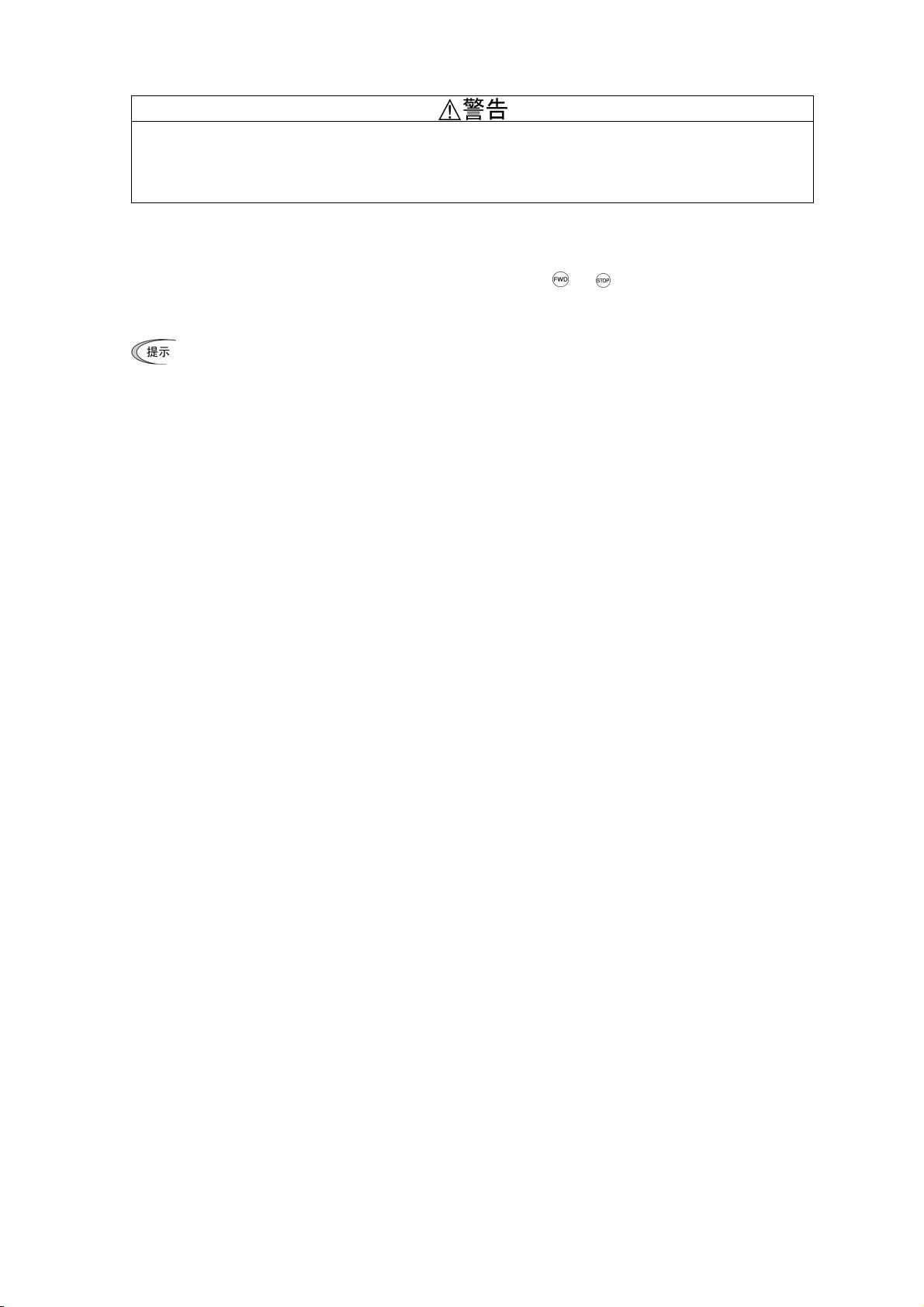

富士变频器FRENIC-VG系列是专为控制三相电动机变速运行设计的设备。用户在使用前必须详细阅读并理解使用说明书,以避免操作不当导致的设备故障或性能下降。变频器的正确使用对于设备的正常运转和寿命至关重要。说明书特别强调,应将手册交给实际操作的最终用户,并且手册需伴随设备直至报废。

说明书提醒用户,某些选配件的使用方法不在本手册中详细说明,需参考相应的选配件手册。此外,FRENIC-VG的主要功能在此手册中有记载,但更详尽的信息则可在用户手册中找到。富士电机株式会社保留对说明书的所有权,禁止未经授权的复制或转贴。

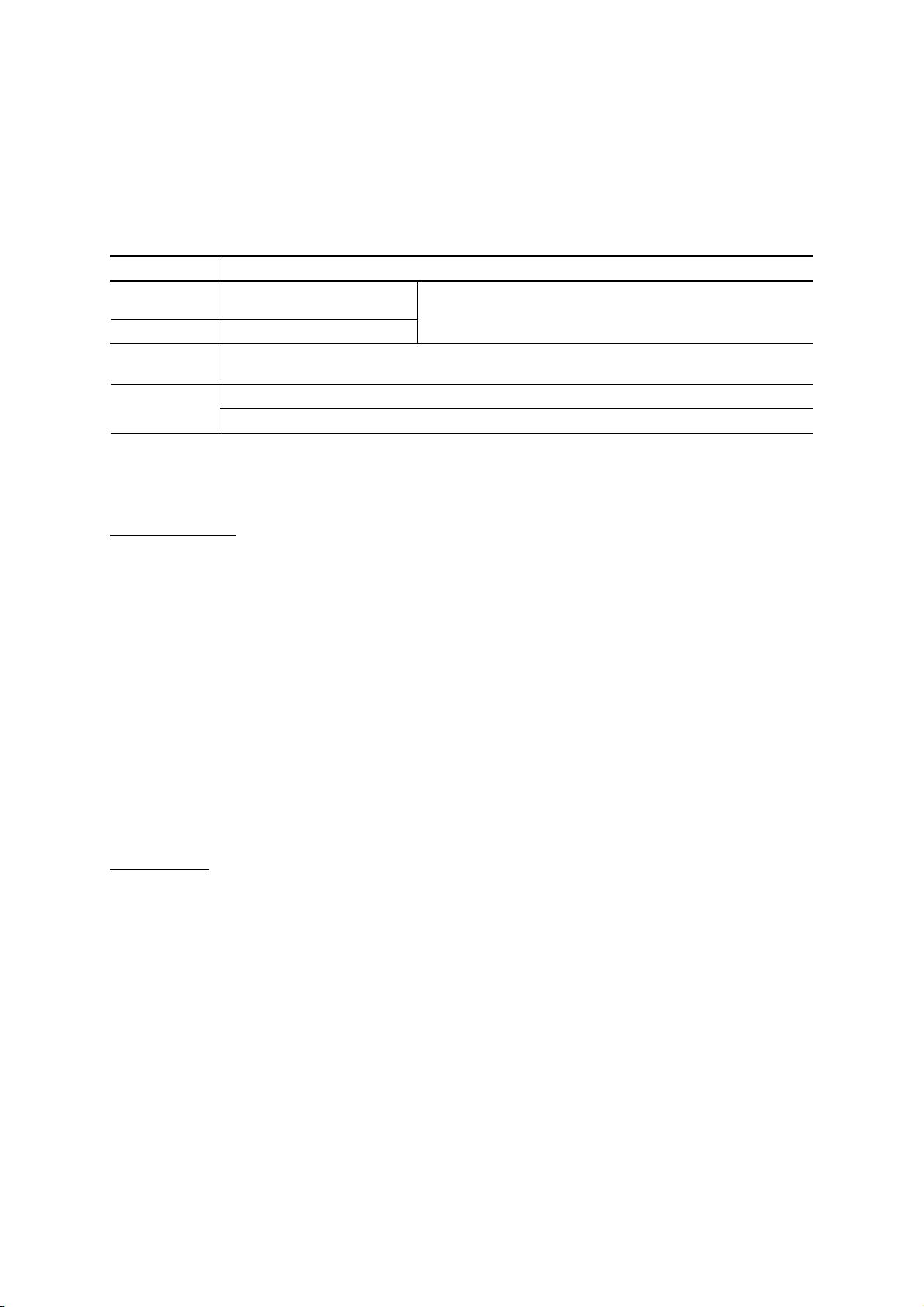

关于高次谐波抑制,手册提到了与高压或特高压用电设备相关的应用,用户可参阅《FRENIC-VG用户手册》的“附录”获取更多信息。手册的"安全注意事项"部分从安装环境、保管环境以及外围设备连接等方面提供了详细的指导。

在安装环境方面,用户需要注意合适的温度、湿度、尘埃等级以及振动情况,以确保变频器的稳定工作。在保管环境中,区分了暂时和长期保管的注意事项,包括防潮、防尘和防高温。

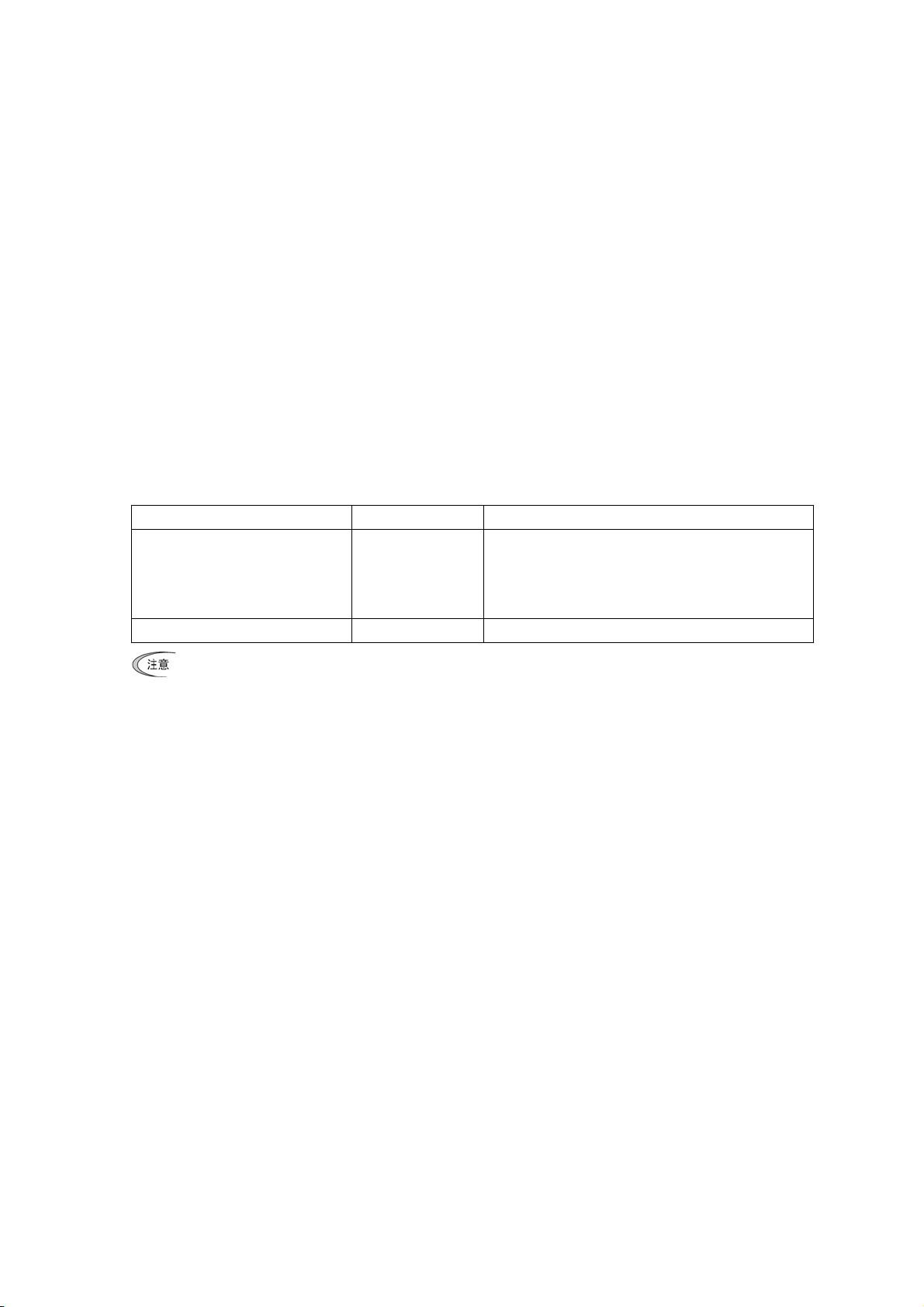

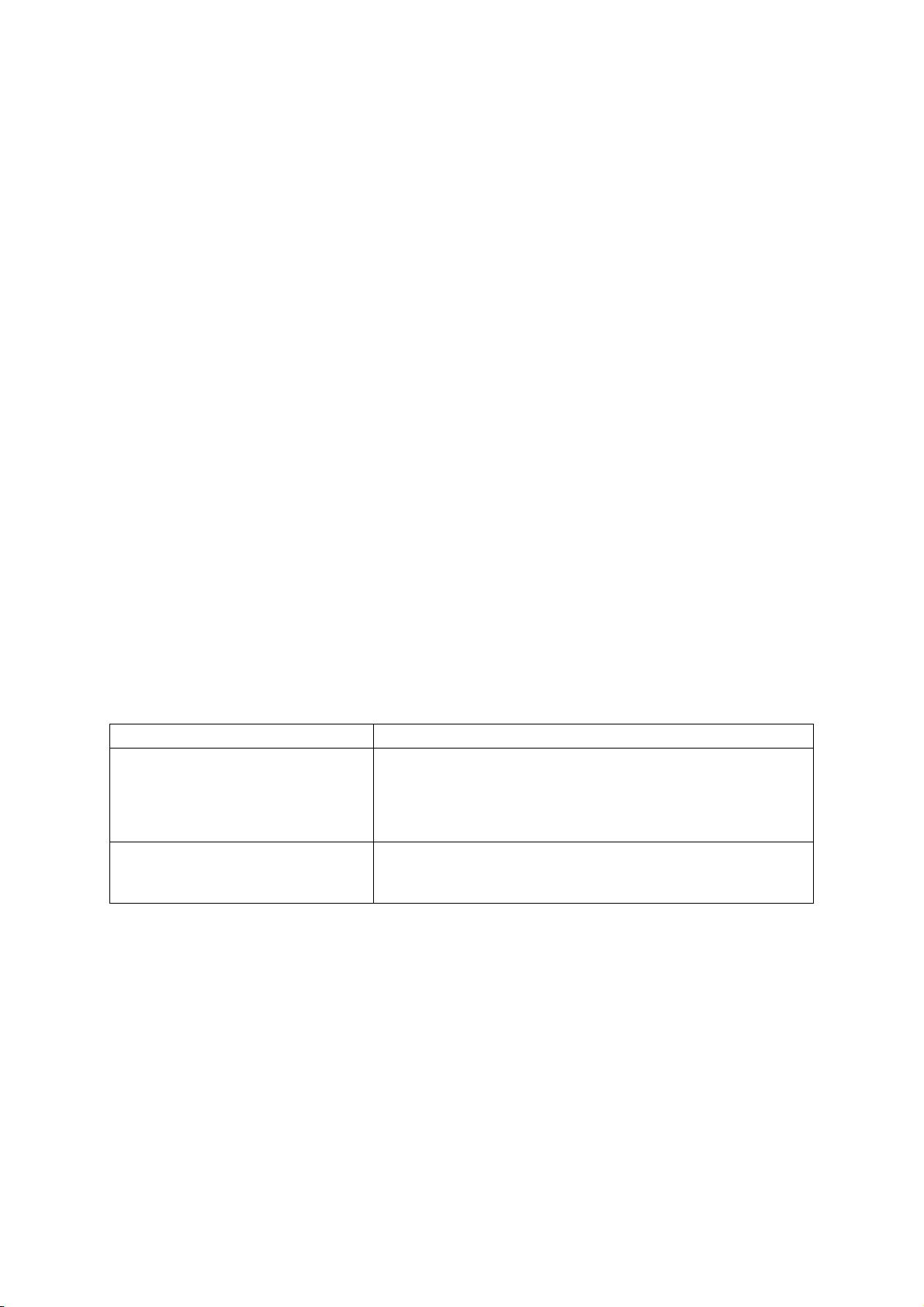

在与外围设备连接时,变频器不能与进相电容器直接连接,电源系统中可能需要直流或交流电抗器来改善输入功率因数。同时,推荐使用适当的断路器和电磁接触器进行保护,以及考虑浪涌吸收器和抑制器的安装以防止电压波动对设备的影响。

干扰对策部分,手册提到了如何减少电磁干扰,确保变频器和其他设备之间的兼容性。这些详细的信息旨在帮助用户实现安全、高效且可靠的变频器运行。

2021-09-29 上传

2021-04-23 上传

2013-09-17 上传

2023-06-11 上传

2024-08-03 上传

2024-11-07 上传

2023-12-21 上传

2023-07-14 上传

2024-03-07 上传

2023-05-24 上传

RONLIN

- 粉丝: 0

- 资源: 1

最新资源

- 飞利浦彩色电视机开关电源的维修.zip

- CODESYS 3.5 SP4.zip

- 全网更新1990-2021我国省级绿色金融发展指数合集

- Advanced_Descriptors-2.2.4-cp37-cp37m-win_amd64.whl.zip

- 城市礼花绽放flash动画

- gae-migrations

- Python库 | doc2dash-2.0.2.tar.gz

- 行业资料-电子功用-光电转换器集成检测方法及系统的说明分析.rar

- simple-fork-join:ForkJoin的简单示例

- lodToolkit 细节级别工具包(LTK)源码需要build(GitHub搬运)

- Kmon:使用 OpenDMK (JMX 2.0) 的 Kafka Monitor

- 售价仅为5美元的可编程小型Web服务器

- 机械设计大理石板自动开槽机(sw18可编辑+PDF)非常好的设计图纸100%好用.zip

- SDC并购数据-汤姆森全球并购数据库

- post-and-page-builder:WordPress 的 Post 和 Page Builder 插件

- 【WordPress插件】2022年最新版完整功能demo+插件v4.2.1.zip