FPGA实现的Turbo码编译码系统设计与优化

版权申诉

"该文档是关于Turbo码编译码系统设计及其FPGA实现的硕士学位论文,探讨了Turbo码的编码与译码算法,并详细阐述了如何在FPGA上进行硬件实现。文中对多种译码算法进行了分析,最终选择了Log-MAP算法,并对其进行了优化以节省硬件资源和降低延迟。论文还涉及编码器中延时模块的改进和E函数的查找表实现方法,以降低系统的运算复杂度。最后,通过Quartus II软件进行了仿真验证,证明所实现的Turbo码译码器具有良好的误码性能和实用价值。关键词包括:Turbo码、Log-MAP算法、软判决和FPGA。"

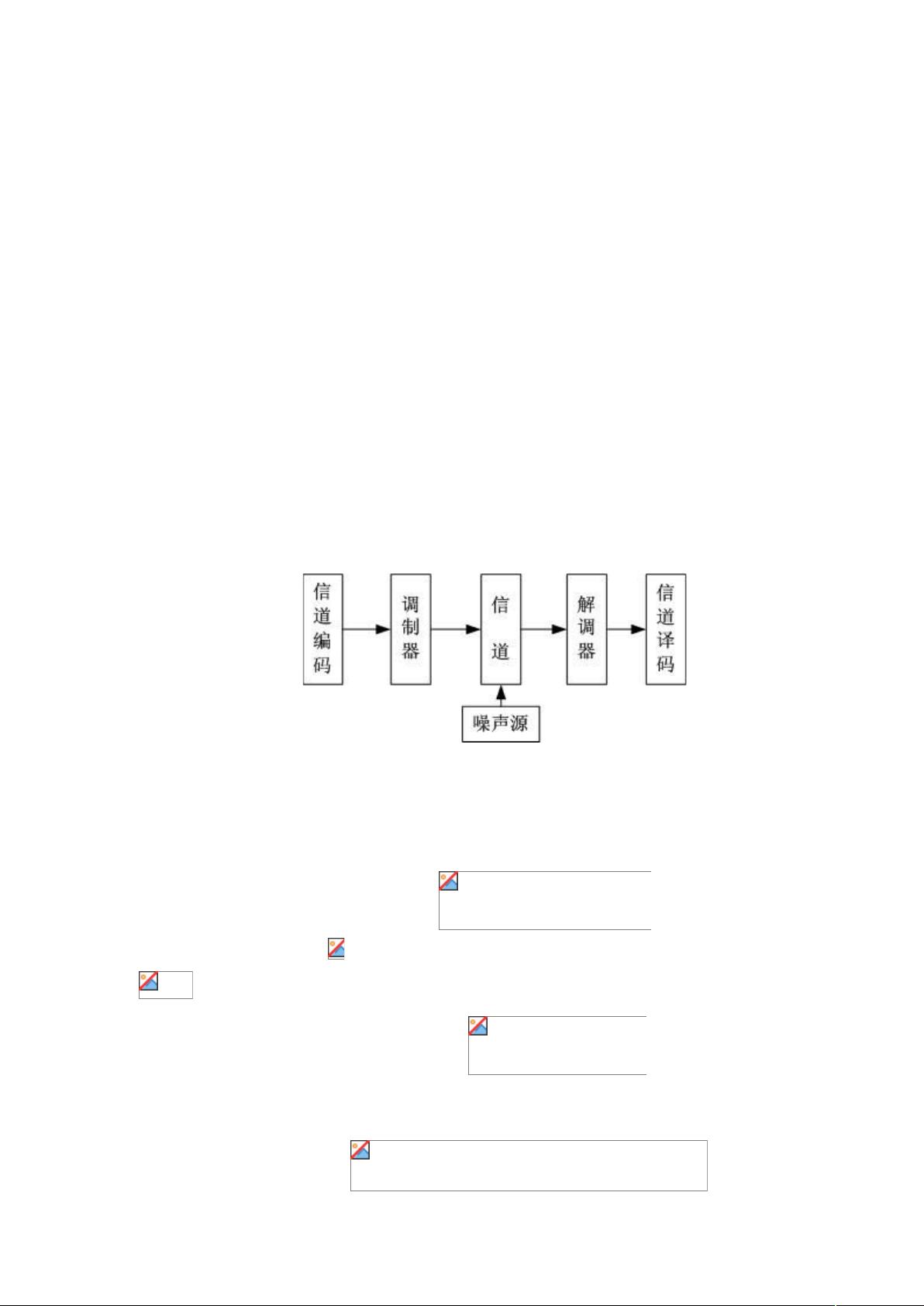

在通信领域,Turbo码是一种强大的纠错编码技术,它的出现极大地提升了在低信噪比环境下的数据传输质量。Turbo码的优越性在于其接近Shannon限的解码性能,这使得它在卫星通信、无线通信、光通信等多个领域有着广泛的应用。

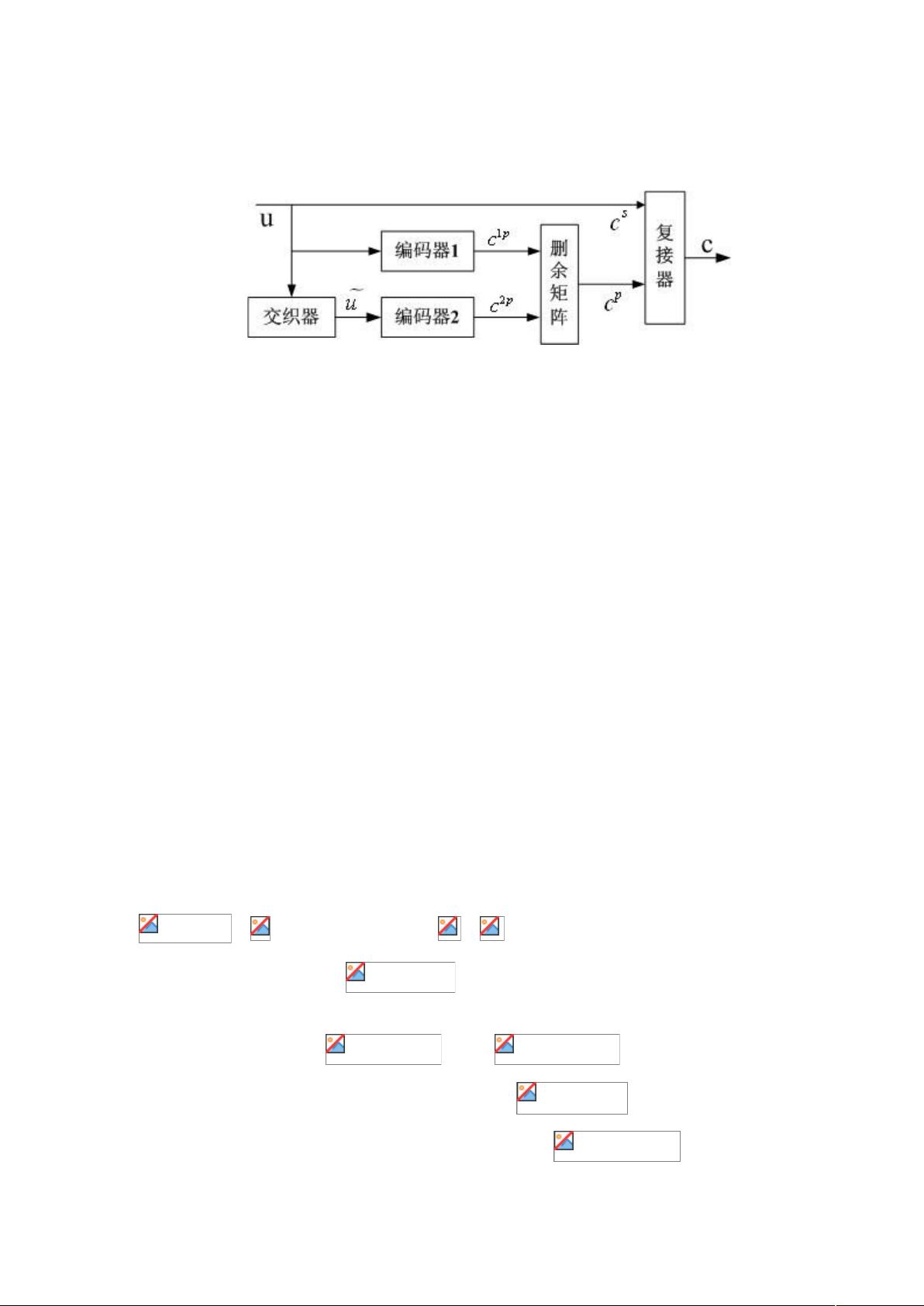

本论文首先回顾了Turbo码的研究背景及国内外的发展状况,然后深入讲解了Turbo码的基本编译码原理。Turbo码的核心是迭代解码,涉及到的主要算法包括最大后验概率(MAP)算法、最大逻辑-最大后验概率(Max-Log-MAP)算法、逻辑-最大后验概率(Log-MAP)算法以及状态合并和输出投票算法(SOVA)。在对比各种算法的性能后,论文选择了Log-MAP算法,因为它在性能和计算复杂度之间找到了较好的平衡。

在FPGA实现方面,设计者采用了“自上而下”和“自下而上”相结合的设计策略,将Turbo码译码器划分为Log-MAP译码单元、交织/解交织器和控制信号产生模块三个主要部分。为了提高效率并减少硬件资源的占用,Log-MAP算法的实现中对计算顺序进行了调整。同时,论文中提出了一种新的延时模块实现方式,类似于交织器,提高了编码精度。在译码器中,通过查找表实现了复杂的E函数,大大降低了运算复杂度。

最后,通过Quartus II软件进行的仿真验证表明,该设计的Turbo码编译码系统在误码性能上表现出色,具备实际应用的价值。这进一步证实了FPGA作为高速、灵活的硬件平台,是实现高效Turbo码编译码的理想选择。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2022-06-01 上传

2021-07-13 上传

zpl19880112

- 粉丝: 9

- 资源: 3万+

最新资源

- Python-2.5.tgz

- lengguanyuantiaoguang.zip_单片机开发_C/C++_

- the_corn_horn

- 易语言农历工具-易语言

- SoftwareEngine:Windows Store应用程序中的软件3D渲染引擎

- docker-laravel-s3-example

- PPT欧美风格57.zip

- 基于UCOS和STM32的ADC采样_stm32ucosII_

- python-3.12.1-embed-arm64.zip

- 易语言图片不规则变形源码-易语言

- 31.rar_matlab例程_PDF_

- PPT静态精选99.zip

- FrontEnd_Assignment:我已经使用ReactJS创建了简单的画布应用程序

- matlab分时代码-neuroconda:在Python,R等中进行神经成像分析的Conda环境

- 第1章 无线信道:传播和衰落_无线信道_

- 易语言取文本串声母源码-易语言