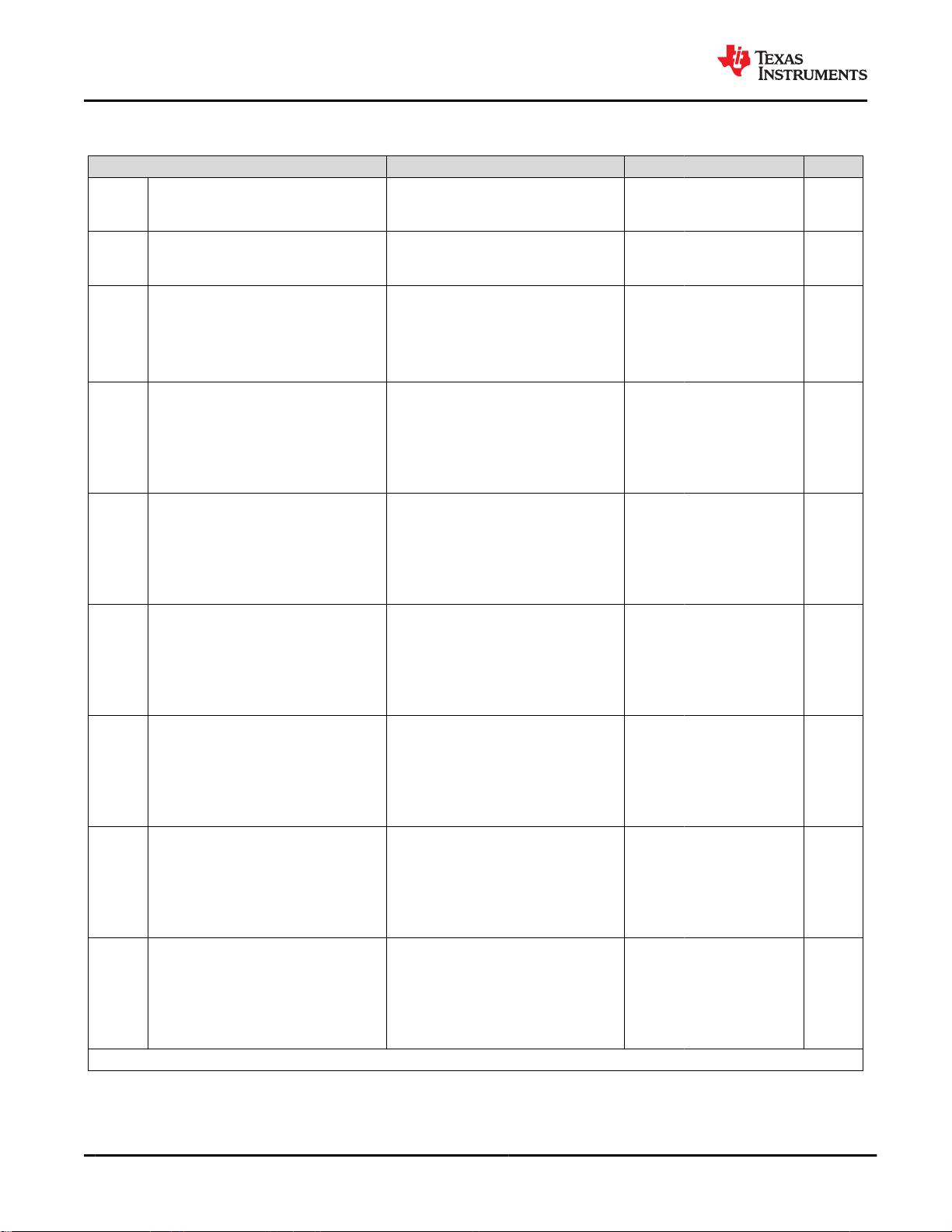

6.7 Switching Characteristics (continued)

over recommended voltage and operating free-air temperature range (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

t

SK1(T)

Clock lane Intra-pair output skew with

worse case skew at inputs

At TTP4; With 0.15 UI skew at input; At 6

Gbps with 150 MHz clock; TX termination

100-Ω; Linear mode;

0.15 UI

t

SK1(T)

Data lane Intra-pair output skew with

worse case skew at inputs

At TTP4; With 0.15 UI skew at input; At

12 Gbps; LTP5, 6, 7, or 8; TXFFE0; TX

termination 100-Ω; Linear mode;

0.15 UI

t

SK1(T)

Clock lane Intra-pair output skew with

zero intra-pair skew at inputs

At TTP4; No intra-pair skew at input; 6

Gbps with 150 MHz clock; TX termination

100-Ω; Limited mode;

0.10 0.15 UI

t

SK1(T)

Data lane Intra-pair output skew with zero

intra-pair skew at inputs

At TTP4; No intra-pair skew at input; At

12 Gbps; LTP5, 6, 7, or 8; TXFFE0; TX

termination 100-Ω; Limited mode;

0.053 0.11 UI

t

SK2(T)

Inter-pair output skew

At TTP4; At 12 Gbps; LTP5, 6, 7, or 8;

TXFFE0;

30 ps

t

RF-CLK-14

Transition time (rise and fall time) for

clock lane when operating at HDMI1.4

At TTP4; 20% to 80%; Clock Frequency =

300 MHz;

75 600 ps

t

RF-CLK-20

Transition time (rise and fall time) for

clock lane when operating at HDMI 2.0

At TTP4; 20% to 80%; Clock Frequency =

150 MHz;

75 600 ps

t

RF_14

Transition time (rise and fall time) for data

lanes when operating at HDMI 1.4

At TTP4; 20% to 80%; DR = 3 Gbps;

SLEW_HDMI14 = default; PRBS7

pattern; Clock Frequency = 300 MHz;

75 195 ps

t

RFDAT_20

Transition time (rise and fall time) for data

lanes when operating at HDMI 2.0

At TTP4; 20% to 80%; DR = 6 Gbps;

SLEW_HDMI20 = default; PRBS7

pattern; Clock Frequency = 150 MHz;

42.5 115 ps

t

SLEW_FRL

Single-ended TX slew rate for data lanes

when operating at HDMI 2.1 FRL

At TTP4; Slope at 50% level; All FRL DR

up to 12 Gbps; SLEW_HDMI21 = Default;

clock pattern of 128 zeros and 128 ones;

16 mV/ps

t

TRANS_3G

Transistion bit duration when de-

emphasis/pre-emphasis is enabled

At TTP4; DR = 3 Gbps; Clock pattern of

128 zeros followed by 128 ones;

0.4 1 UI

t

TRANS_6G

Transistion bit duration when de-

emphasis/pre-emphasis is enabled

At TTP4; DR = 6 Gbps; Clock pattern of

128 zeros followed by 128 ones;

0.4 1 UI

t

TRANS_8G

Transistion bit duration when de-

emphasis/pre-emphasis is enabled

At TTP4; DR = 8 Gbps; Clock pattern of

128 zeros followed by 128 ones;

0.4 1 UI

t

TRANS_10

G

Transistion bit duration when de-

emphasis/pre-emphasis is enabled

At TTP4; DR = 10 Gbps; Clock pattern of

128 zeros followed by 128 ones;

0.5 1.1 UI

t

TRANS_12

G

Transistion bit duration when de-

emphasis/pre-emphasis is enabled

At TTP4; DR = 12 Gbps; Clock pattern of

128 zeros followed by 128 ones;

0.6 1.3 UI

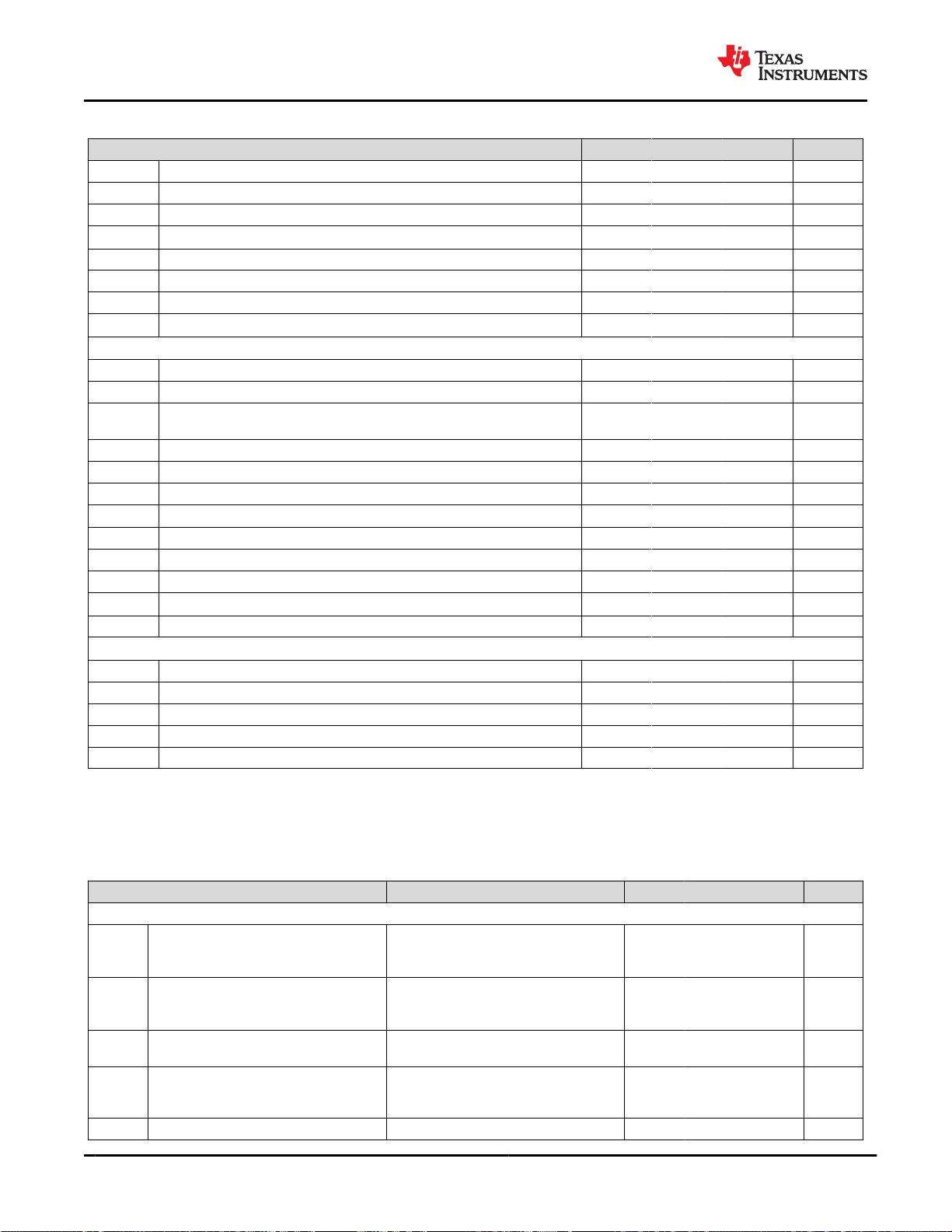

HPD

t

HPD_PD

HPD_IN to HPD_OUT propagation delay

Refer to 图 7-7

100 µs

t

HPD_PWR

DOWN

HPD_IN debounce time before declaring

Powerdown. Enter Powerdown if

HPD_IN is low after debounce time.

Refer to 图 7-7

2 4 ms

t

HPD_STAN

DBY

HPD_IN debounce time required for

exiting Powerdown to Standby. Exit

Powerdown if HPD_IN is high after

debounce time.

Refer to 图 7-8

2 4 ms

Standby

t

STANDBY_

ENTRY

Detection of electrical idle to entry into

Standby.

HPD_IN = H; 300 µs

t

SIGDET_D

B

Maximum differential signal glitch time

rejected during debounce before

transitioning from standby to active

HPD_IN = H; 25 µs

www.ti.com.cn

TMDS1204

ZHCSQV9 – AUGUST 2022

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

15

Product Folder Links: TMDS1204