高速接口:CML、PECL与LVDS互连详解及其应用策略

需积分: 15 84 浏览量

更新于2024-10-10

收藏 389KB PDF 举报

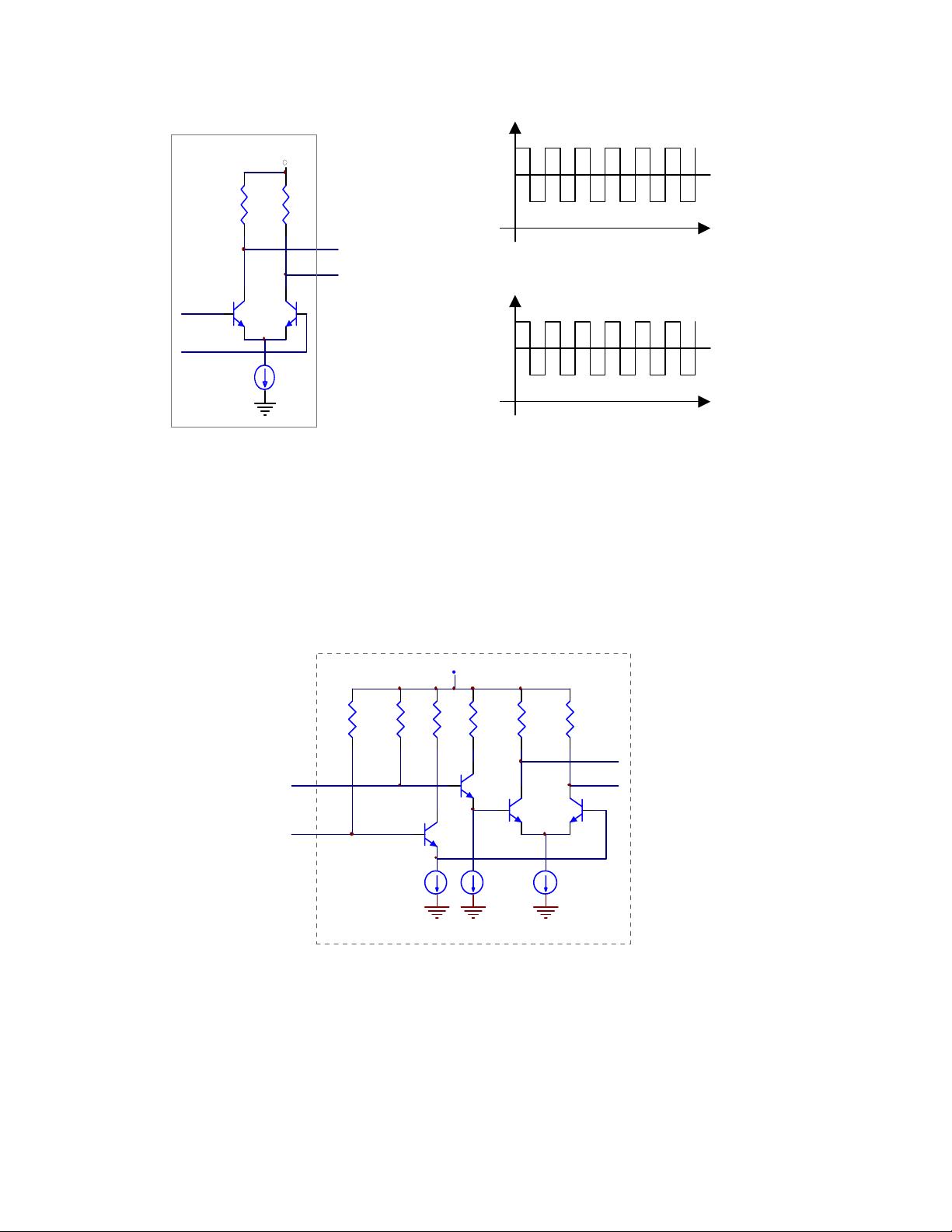

本文主要探讨了CML(电流模式逻辑)、PECL(Positive Emitter-Coupled Logic)和LVDS(Low-Voltage Differential Signals)三种常用高速数字接口标准在实际应用中的互相连接策略。随着现代电子产品对高速数据传输的需求提升,解决不同接口芯片间的高效且低功耗连接显得尤为重要。

CML是一种利用电流来传输信息的逻辑技术,通过改变电流的大小来表示二进制信号,特别适合长距离传输,因为它能提供良好的噪声抑制特性。然而,由于CML信号依赖于电流源,因此对负载敏感,需要精确的匹配才能保持信号质量。

PECL接口是从ECL(Emitter-Coupled Logic)发展而来,简化了负电源的设计,使得电路更加紧凑,适合高速数据的串行或并行连接。它的输出结构包括一个差分对和一对工作在正电源范围内的射随器,输出阻抗低,具有强大的驱动能力。然而,传输线上的阻抗不匹配可能导致信号失真,如振铃现象。

LVDS是一种低电压差分信号接口,设计用于减小电源电压,降低功耗,同时保持信号完整性。它通常用于长距离的高速数据传输,因为其具有较低的信号上升时间、下降时间和电源电压范围,使得信号在传输过程中受噪声影响较小。

在实际应用中,连接CML、PECL和LVDS时,需要考虑以下几个关键因素:

1. 直流偏置:每个接口都有特定的静态电压要求,例如PECL的输出需要偏置到VCC-1.3V,输入则需要高阻抗差分对。连接时需要确保正确的偏置电压以防止信号失真。

2. 负载匹配:CML和PECL的低阻抗特性要求精确的负载匹配,以防止信号衰减或反射。LVDS则通常对负载电阻变化容忍度较高,但仍需注意阻抗一致性。

3. 信号完整性:在长线路中,需要考虑电缆的特性阻抗、串扰和信号反射的影响,可能需要使用阻抗匹配器、终端负载或缓冲器来优化信号传输。

4. 噪声抑制:CML和LVDS因其设计特性,对于噪声抑制较为有效,但在连接过程中,需要尽可能减少噪声源,并采取适当的屏蔽措施。

5. 标准兼容性:选择合适的接口转换器或适配器,以确保不同接口之间的信号转换能够在规定的速率和电压范围内顺利进行。

理解并掌握CML、PECL和LVDS接口的工作原理和连接规则,是实现高速、低功耗和噪声敏感系统设计的关键。实际应用中需要根据具体场景灵活运用,结合器件特性进行优化设计。

2009-02-02 上传

2010-02-02 上传

2023-12-25 上传

2022-09-24 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情