高速互连技术:CML、PECL与LVDS接口详解及其连接策略

需积分: 10 98 浏览量

更新于2024-09-16

收藏 339KB PDF 举报

随着现代数字通信技术的发展,高速数据传输的需求推动了芯片间互连技术的进步。本文主要关注三种常见的高速接口标准:PECL(Positive Emitter-Coupled Logic)、LVDS(Low-Voltage Differential Signals)和CML(Current Mode Logic),它们在低功耗和噪声抑制方面起着关键作用。在设计高速数字系统时,理解这些接口的特性和连接方式至关重要。

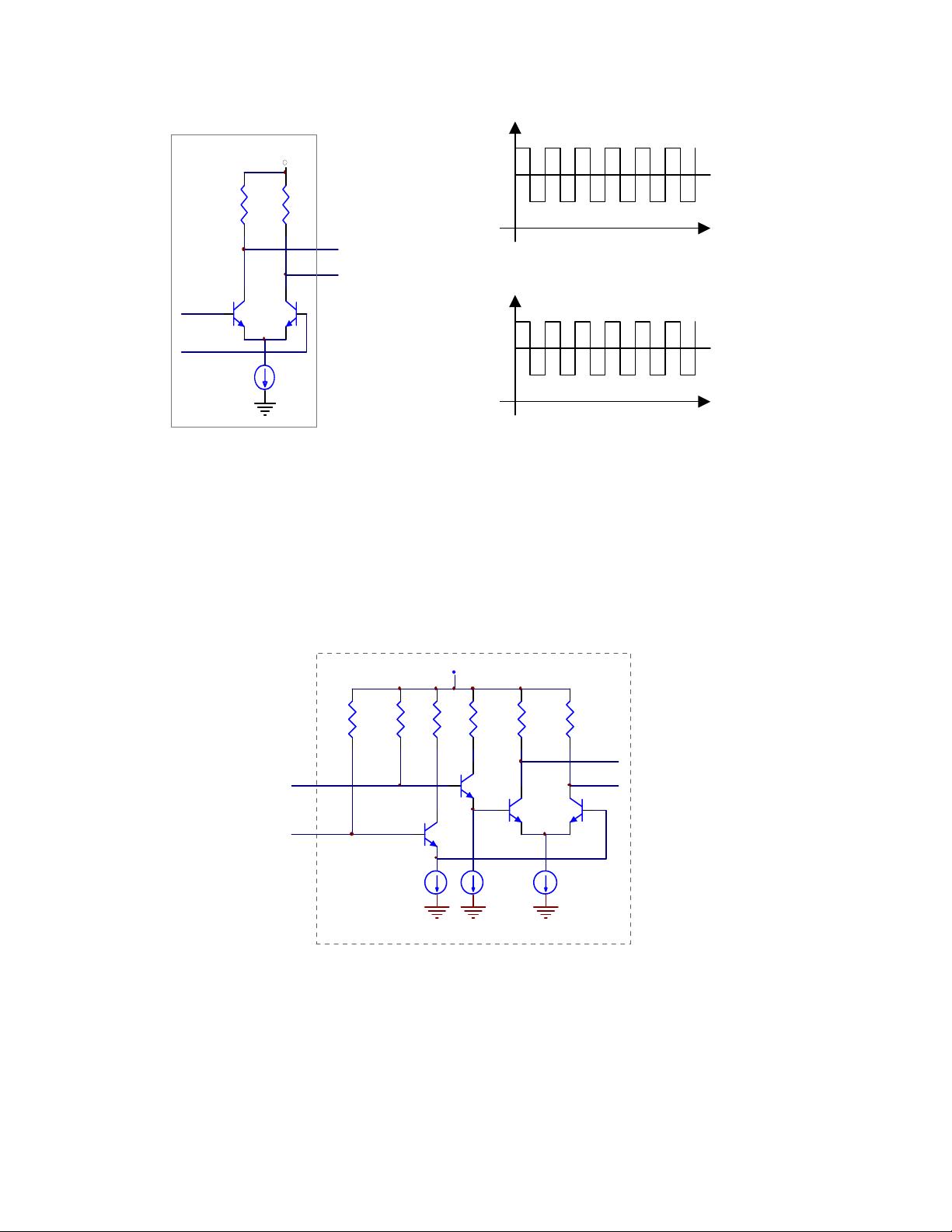

PECL接口源于ECL标准,简化了设计,去除了负电源,使得其在实际应用中更为便利。尽管信号摆幅相对较小,但PECL适合高速串行或并行数据传输。输出结构包含一个差分对和一对缓冲器,工作在正电源范围内,能提供稳定的电流输出,标准负载为50欧姆至VCC-2V。然而,低阻抗可能导致传输线上的失配问题,造成信号时域振铃。

PECL的输入结构则是一个高输入阻抗的差分对,需要对共模电压进行适当的偏置(VCC-1.3V),以确保接收信号的最大动态范围。MAXIM公司提供两种类型的PECL输入电路,一种内置偏置,如MAX3867和MAX3675,另一种则需要外部直流偏置电路。

LVDS是一种低电压差分信号接口,它通过减小电压差来实现低功耗,同时保持信号质量。LVDS接口设计旨在减小电源噪声,提高抗干扰能力,适用于长距离和多层板布线。连接LVDS接口时,必须考虑匹配电阻和终端负载,以防止信号反射和失真。

CML(Current Mode Logic)则是基于电流传输的逻辑,它利用电流信号而不是电压,从而降低功耗,适合长线驱动。然而,CML的设计通常要求严格的线阻抗控制和精确的直流偏置。

设计高速数字系统时,选择合适的接口标准、理解其工作原理以及正确连接不同的芯片是至关重要的。工程师需要根据应用场景和性能要求,合理选择和配置PECL、LVDS和CML等接口,以实现高效、低功耗的数据传输。

2015-07-14 上传

2010-02-02 上传

2023-12-25 上传

2022-09-24 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

巴山夜雨_Stanley

- 粉丝: 0

- 资源: 1

最新资源

- 前端协作项目:发布猜图游戏功能与待修复事项

- Spring框架REST服务开发实践指南

- ALU课设实现基础与高级运算功能

- 深入了解STK:C++音频信号处理综合工具套件

- 华中科技大学电信学院软件无线电实验资料汇总

- CGSN数据解析与集成验证工具集:Python和Shell脚本

- Java实现的远程视频会议系统开发教程

- Change-OEM: 用Java修改Windows OEM信息与Logo

- cmnd:文本到远程API的桥接平台开发

- 解决BIOS刷写错误28:PRR.exe的应用与效果

- 深度学习对抗攻击库:adversarial_robustness_toolbox 1.10.0

- Win7系统CP2102驱动下载与安装指南

- 深入理解Java中的函数式编程技巧

- GY-906 MLX90614ESF传感器模块温度采集应用资料

- Adversarial Robustness Toolbox 1.15.1 工具包安装教程

- GNU Radio的供应商中立SDR开发包:gr-sdr介绍