Version 1.02.00 r0.07 30-Mar-2010 DRAFT MIPI Alliance Specification for DSI

Copyright © 2005-2010 MIPI Alliance, Inc. All rights reserved.

MIPI Alliance Member Confidential.

19

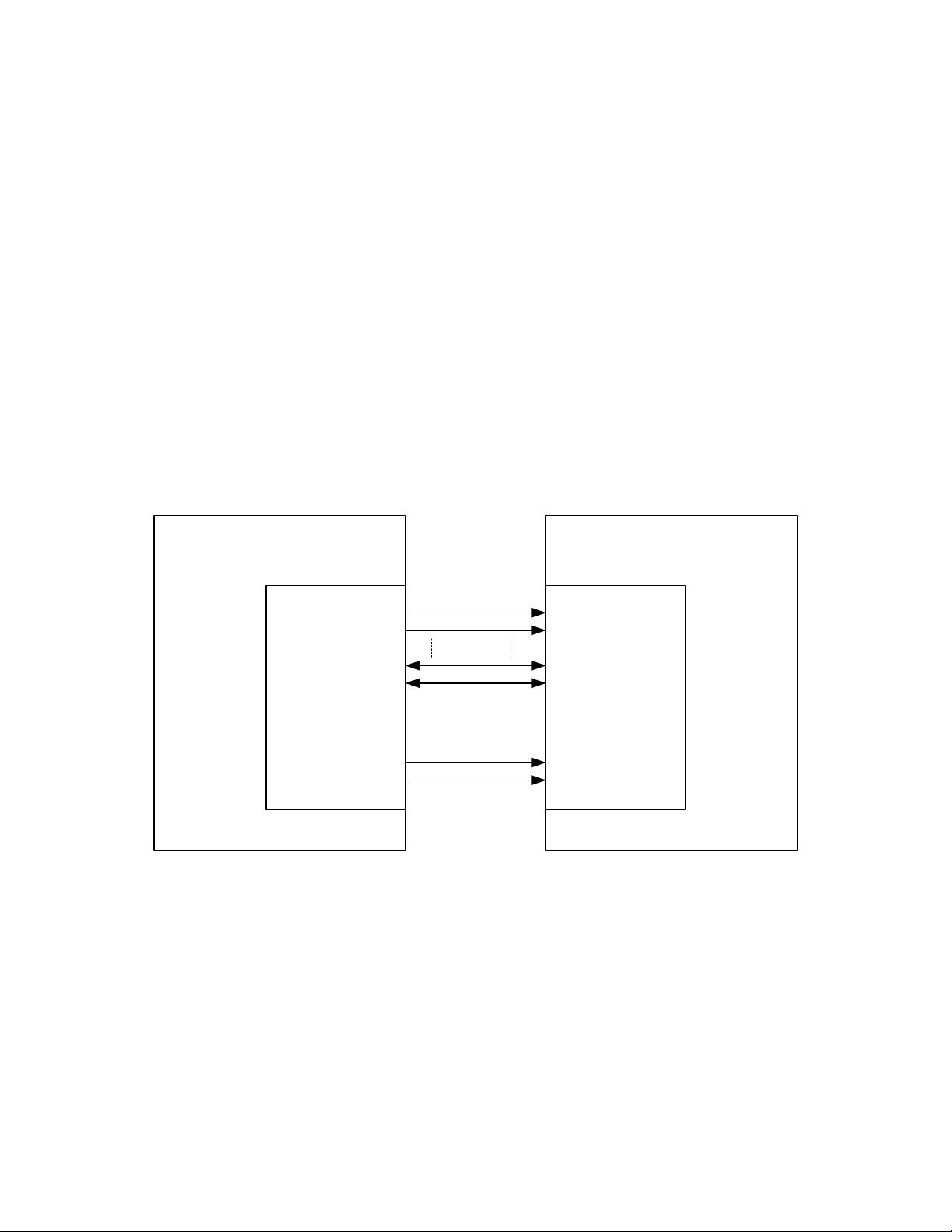

receiving end, the interface collects bytes from the Lanes and merges them together into a recombined data 490

stream that restores the original stream sequence (“merger” function). 491

Protocol Layer: At the lowest level, DSI protocol specifies the sequence and value of bits and bytes 492

traversing the interface. It specifies how bytes are organized into defined groups called packets. The 493

protocol defines required headers for each packet, and how header information is generated and interpreted. 494

The transmitting side of the interface appends header and error-checking information to data being 495

transmitted. On the receiving side, the header is stripped off and interpreted by corresponding logic in the 496

receiver. Error-checking information may be used to test the integrity of incoming data. DSI protocol also 497

documents how packets may be tagged for interleaving multiple command or data streams to separate 498

destinations using a single DSI. 499

Application Layer: This layer describes higher-level encoding and interpretation of data contained in the 500

data stream. Depending on the display subsystem architecture, it may consist of pixels having a prescribed 501

format, or of commands that are interpreted by the display controller inside a display module. The DSI 502

specification describes the mapping of pixel values, commands and command parameters to bytes in the 503

packet assembly. See [MIPI01]. 504

4.2 Command and Video Modes 505

DSI-compliant peripherals support either of two basic modes of operation: Command Mode and Video 506

Mode. Which mode is used depends on the architecture and capabilities of the peripheral. The mode 507

definitions reflect the primary intended use of DSI for display interconnect, but are not intended to restrict 508

DSI from operating in other applications. 509

Typically, a peripheral is capable of Command Mode operation or Video Mode operation. Some Video 510

Mode display modules also include a simplified form of Command Mode operation in which the display 511

module may refresh its screen from a reduced-size, or partial, frame buffer, and the interface (DSI) to the 512

host processor may be shut down to reduce power consumption. 513

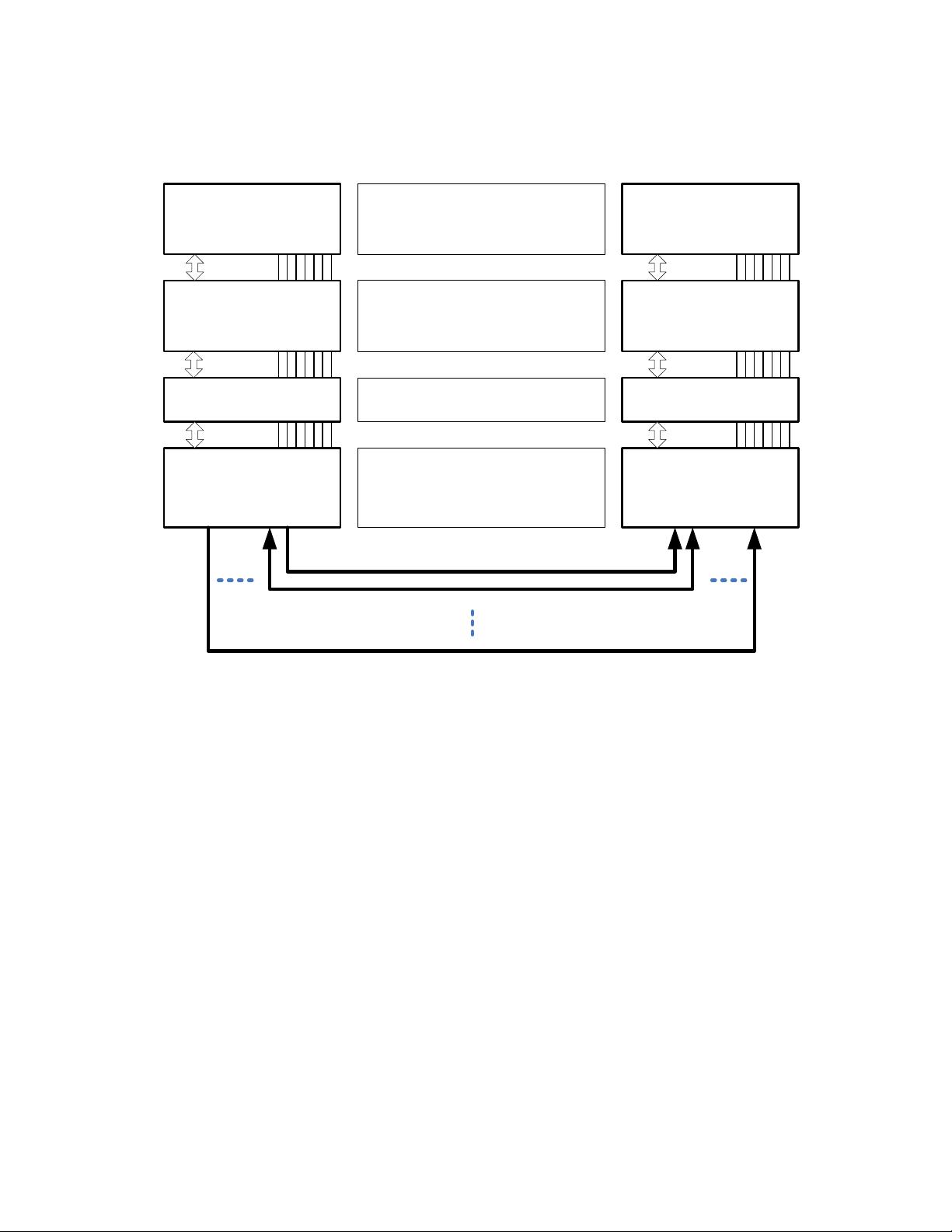

4.2.1 Command Mode 514

Command Mode refers to operation in which transactions primarily take the form of sending commands 515

and data to a peripheral, such as a display module, that incorporates a display controller. The display 516

controller may include local registers and a frame buffer. Systems using Command Mode write to, and read 517

from, the registers and frame buffer memory. The host processor indirectly controls activity at the 518

peripheral by sending commands, parameters and data to the display controller. The host processor can also 519

read display module status information or the contents of the frame memory. Command Mode operation 520

requires a bidirectional interface. 521

4.2.2 Video Mode Operation 522

Video Mode refers to operation in which transfers from the host processor to the peripheral take the form of 523

a real-time pixel stream. In normal operation, the display module relies on the host processor to provide 524

image data at sufficient bandwidth to avoid flicker or other visible artifacts in the displayed image. Video 525

information should only be transmitted using High Speed Mode. 526

Some Video Mode architectures may include a simple timing controller and partial frame buffer, used to 527

maintain a partial-screen or lower-resolution image in standby or Low Power Mode. This permits the 528

interface to be shut down to reduce power consumption. 529

To reduce complexity and cost, systems that only operate in Video Mode may use a unidirectional data 530

path. 531